- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Intel FPGA community members,

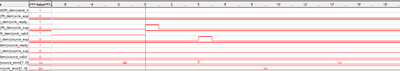

I am getting a strange error from the Intel FFT FPGA IP. The waveform from Signal Tap Logic analyzer is below:

I am raising the sink_valid and sink_sop at the same cycle and sink_sop take 1 cycle and valid stays high. after 4 cycles I get the source_error=1 and source_eop pulsed and nothing comes out afterwards from the module.

I am using a time_limited ip at the moment but this happens just after I download the sof file and run my application. I hope this is not related to ip evaluation mode.

design is running at 250 MHz clock and there is a top level constraint for the clock tree.

I create the fft module with tcl script below and instantiate it in my hierarchy.

What could be possible reason for such a behavior?

I would appreciate if you can help me solving this issue.

package require qsys

# create the system "fft_ip"

proc do_create_fft_ip {} {

# create the system

create_system fft_ip

set_project_property DEVICE {10AX016E3F27I2SG}

set_project_property DEVICE_FAMILY {Arria 10}

set_project_property HIDE_FROM_IP_CATALOG {true}

set_use_testbench_naming_pattern 0 {}

# add the components

add_instance fft_ii_0 altera_fft_ii 19.1

set_instance_parameter_value fft_ii_0 {data_flow} {Streaming}

set_instance_parameter_value fft_ii_0 {data_rep} {Block Floating Point}

set_instance_parameter_value fft_ii_0 {design_env} {NATIVE}

set_instance_parameter_value fft_ii_0 {direction} {Bi-directional}

set_instance_parameter_value fft_ii_0 {dsp_resource_opt} {0}

set_instance_parameter_value fft_ii_0 {engine_arch} {Quad Output}

set_instance_parameter_value fft_ii_0 {hard_fp} {0}

set_instance_parameter_value fft_ii_0 {hyper_opt} {0}

set_instance_parameter_value fft_ii_0 {in_order} {Natural}

set_instance_parameter_value fft_ii_0 {in_width} {16}

set_instance_parameter_value fft_ii_0 {length} {8192}

set_instance_parameter_value fft_ii_0 {num_engines} {4}

set_instance_parameter_value fft_ii_0 {out_order} {Natural}

set_instance_parameter_value fft_ii_0 {out_width} {29}

set_instance_parameter_value fft_ii_0 {twid_width} {16}

set_instance_property fft_ii_0 AUTO_EXPORT true

# add wirelevel expressions

# add the exports

set_interface_property clk EXPORT_OF fft_ii_0.clk

set_interface_property rst EXPORT_OF fft_ii_0.rst

set_interface_property sink EXPORT_OF fft_ii_0.sink

set_interface_property source EXPORT_OF fft_ii_0.source

# set the the module properties

set_module_property BONUS_DATA {<?xml version="1.0" encoding="UTF-8"?>

<bonusData>

<element __value="fft_ii_0">

<datum __value="_sortIndex" value="0" type="int" />

</element>

</bonusData>

}

set_module_property FILE {fft_ip.ip}

set_module_property GENERATION_ID {0x00000000}

set_module_property NAME {fft_ip}

# save the system

sync_sysinfo_parameters

save_system fft_ip

}

# create all the systems, from bottom up

do_create_fft_ip

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Omer,

Is there any message or warning you are getting while programming the sof?

Some suggestions

1) Make sure the sof should be generated with the correct device, I mean should match with the signal tap.

2) Try programming the sof through the programmer instead of signal tap, if you are doing so.

3) Power OFF-ON board once, then try.

Please let me know, if you still face any issues.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is the issue resolved?

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear @Kshitij_Intel ,

The sof is generated with the correct device and programmed via programmer and I have restarted the device and I have tried on different HW but Unfortunately no, the issue is not solved. There are the following critical warnings from compilation report: Could those cause such a problem?

Critical Warning(127003): Can't find Memory Initialization File or Hexadecimal (Intel-Format) File /fft_demod_altera_fft_ii_191_vqrjwey_1n4096sin.hex -- setting all initial values to 0

Critical Warning(127003): Can't find Memory Initialization File or Hexadecimal (Intel-Format) File /fft_demod_altera_fft_ii_191_vqrjwey_2n4096sin.hex -- setting all initial values to 0

Critical Warning(127003): Can't find Memory Initialization File or Hexadecimal (Intel-Format) File /fft_demod_altera_fft_ii_191_vqrjwey_3n4096sin.hex -- setting all initial values to 0

Critical Warning(127003): Can't find Memory Initialization File or Hexadecimal (Intel-Format) File /fft_demod_altera_fft_ii_191_vqrjwey_1n4096cos.hex -- setting all initial values to 0

Critical Warning(127003): Can't find Memory Initialization File or Hexadecimal (Intel-Format) File /fft_demod_altera_fft_ii_191_vqrjwey_2n4096cos.hex -- setting all initial values to 0

Critical Warning(127003): Can't find Memory Initialization File or Hexadecimal (Intel-Format) File /fft_demod_altera_fft_ii_191_vqrjwey_3n4096cos.hex -- setting all initial values to 0

Best Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It seems to be a path issue, while generating the IP. Please recheck once. While generating the IP it might be generating some files in hex format which is used as memory initialization.

I would suggest create a new design, give proper paths.

Thank you

Kshitij Goel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

thank you for feedback,

Update:

I have cleaned the design on qsys and not anymore having the warnings above, I also got a full license in meantime so no more time limited sof.

However the problem still exists and I get exactly the same waveform as above attached.

What could I do more to narrow down the problem?

Best Regards,

Ömer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Any other ideas about such an error?

This becomes a blocking issue at the moment for project I am working on. I would appreciate if we can find a solution here.

Best Regards,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

one more update: if I change the FFT parameters to be <fixed_point>, <variable streaming> instead of <block floating point>, <streaming>, it does not generate the error with all the same timing and signals.

But my desired implementation is Block floating point still, so this is to find some more hint about what could have gone wrong.

I appreciate if you can help with the problem.

Best Regards,

Ömer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Can you please share your model to replicate your issue.

Please mention MATLAB version, device OPN, Quartus version, OS platform you are using.

Thank you

Kshitij Goel

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page