- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am using an Arria V GX which is suppose to have 2 hard memory controllers. How do I select which one to activate as the UNIPHY memory controller seems to only work with bank 7 but my memory device is routed to bank 4, which causes a fitter error if I try to use the specified hard memory pins on this bank.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is the fitter error you are getting?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KMich2,

As per you said the device have 2 hard memory controllers (HMC), so I assume you are using Arria V GX A1 or A3 Device.

By right, both Bank 4 and 7 is usable for this device.

May I know what is the data width you used and what type of fitter error you seen?

Just for your reference, you may refer to this handbook (page 264) in below link to get more information on Hard Memory Controller in Arria V device.

https://www.intel.com/content/www/us/en/programmable/documentation/sam1403480004852.html#sam1403479856478

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The device I am using is 5AGXMA3D6F27C6.

The controller width is 32, the DQ bus is 16 bits.

The error messages I am getting are as follows:

Error (175006): Could not find path between the HPHY and destination pin

Info (175027): Destination: pin DDR3_CSn

Info (175015): The I/O pad DDR3_CSn is constrained to the location PIN_W13 due to: User Location Constraints (PIN_W13)

Info (14709): The constrained I/O pad is contained within this pin

Error (175022): The HPHY could not be placed in any location to satisfy its connectivity requirements

Info (175021): The pin was placed in location W13

Info (175029): 1 location affected

Info (175029): MEMPHY_X55_Y90_N1

I assume there must be a setting to make the device on bank 4 the master, but it's not clear what this setting should be or how to enter it, as there is no option to select the device in the UniPHY IP wizard, any advice?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KMich2,

The Arria V HMC use dedicated I/O pins as data, address, command, control, clock, and ground pins for the SDRAM interface. I have highlighted the hard memory interface pin-out in YELLOW in attached pin-out excel file. Therefore, user shouldn’t be assigning hard memory interface DDR3 pin-out to other pin location anymore. Only dedicated pin-out is acceptable.

I suggest you to modified your design by removing all the pin location assignment for DDR3 IP and re-compile your project.

Hope this helps.

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The pin assignments we are using are in accordance to this table, but for the hard memory controller pins shown on IO bank 4, instead of IO bank 7 (which are automatically assigned by the fitter if we do not constrain the pins). As there are two hard memory controller, how do we get the fitter to use the other one, as our memory chip is wired to IO bank 4 and changing our design is not an option for us.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

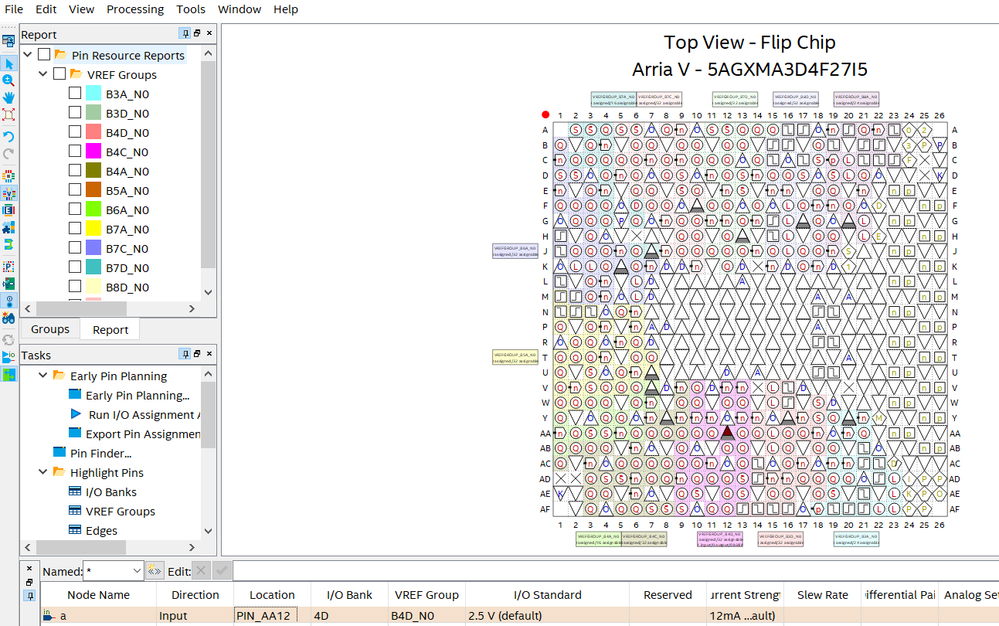

Another question related to this table... How do we invoke the 'optional function' on a pin, for example the VREFB4DN0 on pin AA12. I understand this should be an externally supplied reference voltage for bank 4D at 1/2 the selected IO standard for the bank, but the pin also seems to serve as an IO pin. Do we need to configure the pin to use it as a voltage reference input?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KMich2,

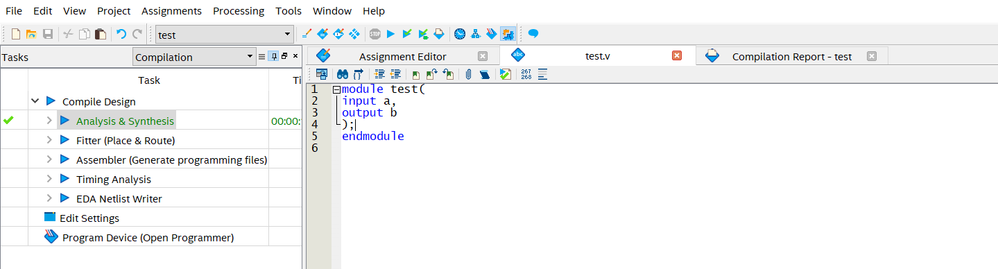

Depending on your design, if you used verilog code then you can set the input pin in your RTL ( as shown in Figure 1) , re-compile the design ( compile at Analysis and Synthesis stage will do) and assign this PIN_AA12 as input in your Pin Planner (Figure 2). Then directly connect the VREF to this PIN_AA12. Make sure also the I/O standard is set accordingly with your design. What shown in Figure below is just an example for your reference. 😊

Figure 1:

Hope this helps.

Thanks

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

OK, so I just need to assign the pin as an input and it will act as a reference for all the other pins on the bank? Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes , you are right.

You are most welcome 😊

Regards,

NAli1

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have found a simple workaround:

By reserving one of the pins allocated for the HMC on bank 7 (e.g. the RZQ pin G6) the alternative HMC on bank 4 is automatically chosen during fitting.

Thank you for your responses.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KMich2,

Glad to know that your design is working now. Thank you for sharing the workaround. It's really helpful for other user that may encounter the same issue in future. Appreciated your sharing . Thanks and have a nice day 😊

Regards,

NAli1

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page