- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

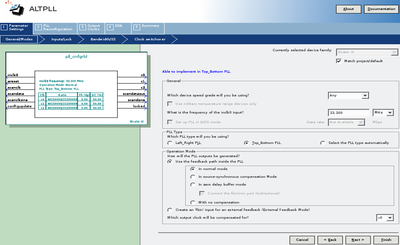

I am tried to converter old pll in quartus 13.1 to quartus pro 21.x

OLD ALLPLT has scanclk/scandataout port from tool .

// synopsys translate_off

`timescale 1 ps / 1 ps

// synopsys translate_on

module pll_cnfgrbl (

areset,

configupdate,

inclk0,

scanclk,

scanclkena,

scandata,

c0,

c1,

c2,

locked,

scandataout,

scandone);

input arese

how to generate same PLL for s10 ?

I can't see scanclk/scankena/scnadata pin option in quartus pro 21.x

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That IP is not compatible with S10. You have to create a new Intel PLL IP for it and copy over the settings. The options you mention may not be available for the newer PLL.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I know that I have to generate,

but how to do for ALLPLL.

in IOLL itel FPGA IP from quatur pro,

doesn't have

scanclk,

scanclkena,

scandata,

these pins.

That is why I don't re-generation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In ALTPLL the scanclk, scandata etc are used for Dynamic Reconfiguration. In S10, PLL is different and the reconfiguration functionality can be achieved using IOPLL Reconfig Intel® FPGA IP Core: https://www.intel.com/content/www/us/en/docs/programmable/683195/20-3/core-references-14991.html

Also, the Dynamic phase shift ports are different: https://www.intel.com/content/www/us/en/docs/programmable/683195/20-3/dynamic-phase-shift-ports-in-the-ip-core.html

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page