- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the platform designer, the ip of altmemddr for ddr2, the signal type of external_connections (local_init_done, reset_phy_clk_n) shares the same name is export, it raises error if this conduits connected to other modules. Is it a bug of this ip? how to handle it?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm not sure I understand. A conduit (or any interface) is exported from a Platform Designer system and is made up of one or more unique signal names that you connect to other parts of your Quartus project or connect directly to I/O pins. When you export any interface (including a conduit) in Platform Designer, you enter a unique name and the individual signals of the exported interface are prefixed with this unique name. Can you post a screenshot of what you are seeing?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

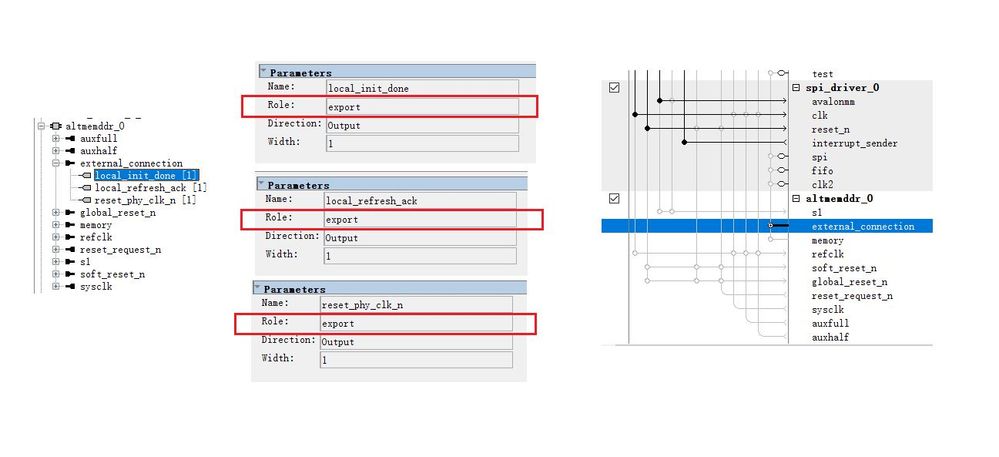

You can see from below picture. There external_conduits of altmemaddr includes 3 outputs , all below 3 outputs use the same signal type is export. I would like to connect these 3 output to other modules inside this NIOS system, it will reports error message because they shares the same name of signal type. I expect there should be no issue if they name it differently, but I can not change this ip.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

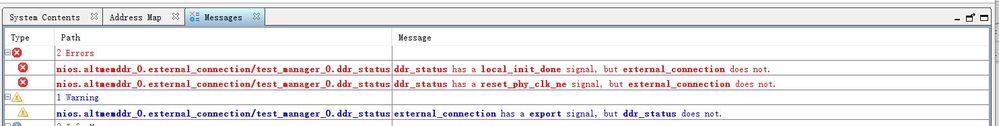

What are the error messages? Can you show the conduit(s) that you are trying to connect this conduit to? Normally, to connect a conduit to a conduit in a system, the signal names must match, as you say. Without seeing the other side or the error messages you're getting, it's hard to diagnose.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Your are right. They should be match, but this ip conduit with 3 signal marked with export, then you can not map with each output. This is the my concern.

In the below picture, the test_manager_0.ddr_status is defined by me with conduit, local_init_done, and reset_phy_clk_n.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @XShen1 ,

Is it possible for you to attach the design so that I reproduce the issue locally and get better understanding of the issue?

Let me know if you have any concern.

Regards,

Aida

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I find it's solved in UniPHY design. So I decided to change to UniPHY design and not plan more action on it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Glad to know the issue is solved 😊 . Thanks for the confirmation. I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page