- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

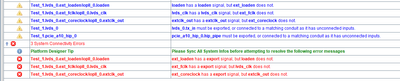

I am using the LVDS SERDES IP with external PLL provided by the IOPLL. I configured the IOPLL as recommended in the LVDS SERDES IP for Cyclone 10 GX but I am getting an error:

"ext_<clock name> has a export signal, but <clock name> does not."

This is true for all three clock input from the IOPLL to the LVDS SERDES.

Any idea on how to fix this?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi @KRoma6

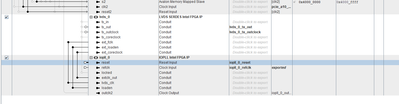

Did you use the PLL setting: Access to PLL LVDS_CLK/LOADEN output port

If yes, could you try this on the RTL instead of the Qsys platform?

Lets narrow down if this is a Qsys platform connectivity issue or an LVDS IP issue.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi JonWay,

Yes I tried both options for the "Access to PLL LVDS_CLK/LOADEN output port": <"LOADEN 0" and "LOADEN 0 & 1">.

So you want to export these signals and connect them within a module?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Generate HDL for both the LVDS and PLL IP. Create a top RTL file and instantiate both IPs there. Connect them together by RTL coding. Check if the problem is still there or not.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page