- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi!

After reading UG-20093 | 2019.12.30, i try to simulate fPLL (fractional PLL - Transceiver mode - 80MHz refclk, 570MHz output freq.) component. I got this error after including libraries and compile fpll instance on /sim directory and after clicking "simulate":

vsim work.pllka

# vsim work.pllka

# Start time: 09:30:05 on Sep 14,2021

# Loading std.standard

# Loading std.textio(body)

# Loading ieee.std_logic_1164(body)

# Loading ieee.numeric_std(body)

# Loading verilog.vl_types(body)

# Loading work.pllka(rtl)

# Loading sv_std.std

# Loading altera_xcvr_fpll_a10_191.alt_xcvr_native_avmm_nf

# ** Error: (vsim-3033) Instantiation of '<protected><protected><protected><protected><protected><protected>' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Protected: /pllka/<protected> File: ../../altera_xcvr_fpll_a10_191/sim/mentor/altera_xcvr_fpll_a10.sv Line: 12

# Searched libraries:

# C:/Users/P2009/Downloads/Nowyfolder4fpll/pllka/pllka/sim/mentor/libraries/work

# ** Error: (vsim-3033) Instantiation of '<protected><protected><protected><protected><protected><protected>' failed. The design unit was not found.

# Time: 0 ps Iteration: 0 Protected: /pllka/<protected> File: ../../altera_xcvr_fpll_a10_191/sim/mentor/altera_xcvr_fpll_a10.sv Line: 12

# Searched libraries:

# C:/Users/P2009/Downloads/Nowyfolder4fpll/pllka/pllka/sim/mentor/libraries/work

# Error loading design

# End time: 09:30:05 on Sep 14,2021, Elapsed time: 0:00:00

# Errors: 2, Warnings: 0

Previosly i created .tcl script in sim/mentor directory:

set QSYS_SIMDIR ../

source $QSYS_SIMDIR/mentor/msim_setup.tcl

dev_com

com

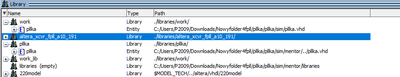

and i typed do <name of my tcl> in console of modelsim. Libraries was succesfully added.:

then i compiling component in sim direcotry, clicking on work-pll i and i get error mentioned above. I am using Quartus Pro 21.2.0.72. Cyclone 10GX project.

Please help!

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Since you are using Quartus Prime Pro edition, you will need to edit your .do file before you simulate your project. From your .do file you are missing a lot of commands:

- Compile all design and testbench files in your project. "vlog -vlog01compat -work work ../<design and testbench files>"

- This is to set the top-level simulation or testbench module/entity name. "set TOP_LEVEL_NAME <simulation top>"

- Call command to elaborate your design and testbench. "elab"

- To run the simulation. "run -a"

You can refer to section 1.4 of this document to understand better: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20093.pdf#page=6

You also need to save your file as wojtek.do instead of wojtek.tcl.

Best regards,

Nurina

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Is the fPLL written by you or did you instantiate it on Quartus?

Do you have a testbench? Can you show us the code for your testbench?

Can you also share your .do file?

Thanks,

Nurina

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi!

I created separated project in order to investigation problem. Previously problem occurs in project which was including all neccessery PHY components - Transceiver PHY, Reset and PLL (fPLL). correctly connected. So i uploading separated project (Nowyfolder5) where only is fPLL component.

Tesbench: fpll_symulacja_test_o

Do file: wojtek.tcl in Nowyfolder5\fpll_o\pllka_o\sim\mentor

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Since you are using Quartus Prime Pro edition, you will need to edit your .do file before you simulate your project. From your .do file you are missing a lot of commands:

- Compile all design and testbench files in your project. "vlog -vlog01compat -work work ../<design and testbench files>"

- This is to set the top-level simulation or testbench module/entity name. "set TOP_LEVEL_NAME <simulation top>"

- Call command to elaborate your design and testbench. "elab"

- To run the simulation. "run -a"

You can refer to section 1.4 of this document to understand better: https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-20093.pdf#page=6

You also need to save your file as wojtek.do instead of wojtek.tcl.

Best regards,

Nurina

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Since your question has been addressed, I now transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Regards,

Nurina

P/S: If you like my comment, feel free to give Kudos. If my comment solved your problem, feel free to accept my comment as solution!