- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi All,

I am using intel NCO IP as DDS to generate a LO for the mixer.

when i am testing my module on board(aria10 eval), i observe that output sample is shifting by one clock (back and forth with each reboot) wrt valid.

this is not observed in the simulation

*output valid comes at fixed latency wrt clken, (10 clks).

this is not observed in the simulation.

iam not able to understand this behavior of IP.

what could be the issue? please suggest.

Thanks.

IP parameters are as follows:

clk =245.76 MHz.

architecture = multiplier based

no of band =1

no of ch =1

clock cyc/output =1

phase acc =18bit

ang resolution =18bit

mag resolution = 16bit

freq mod and phase mod= disabled.

dithering = disabled.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This might be related to the reset, you probably need to hold the reset for a few clock cycles while the clken is asserted.

Regards -SK

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Did you reset the NCO IP after power up? Does the behavior change after each reset?

In order to better understand the problem, it will be helpful if you can attach the waveform of your simulation and hardware result.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SK,

thanks for the response.

This behavior is not very consistent it is coming once in very 8 to 10 reboots.

and output is not just one sample shifted but samples are totally different some times.

Did you reset the NCO IP after power up? Does the behavior change after each reset?

>>Yes NCO gets reset after Power up, but behavior doesn't change at every reset. it changes after reboot.

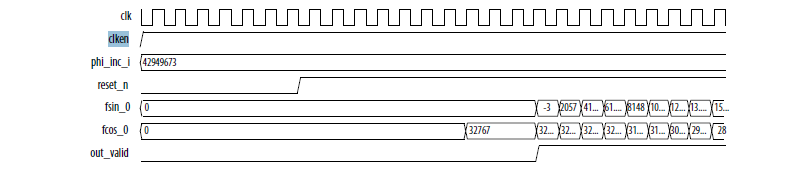

i am attaching the simulation and the signal tap wave form.

simulation captures expected samples .

and signal tap capture change in the behavior

Thanks

Dinker

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you reset the NCO IP after the input clock of NCO is stable? When the problem happens, if you issue a reset, does it remain the same?

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SK

Do you reset the NCO IP after the input clock of NCO is stable? When the problem happens, if you issue a reset, does it remain the same?

>>once clock is stable and module reset is de asserted, i am not resetting the NCO again.

but in simulation i observed that when i force reset in between the behavior is same as observed on board.

thanks & Regards

Dinker

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

This might be related to the reset, you probably need to hold the reset for a few clock cycles while the clken is asserted.

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SK,

Thanks for the reply.

>>This might be related to the reset, you probably need to hold the reset for a few clock cycles while the clken is asserted.

yes, i also feel the same . even data diagram in IP document shows the same.

In my design reset is de asserted long before clken. clken is asserted when i get IQ_in valid.

what if, i reset NCO IP again after the clken is asserted?

I have one concern, that what will happen if NCO ip gets a synchronous reset? (its aspects asynchronous reset).

Thanks.

Regards

Dinker

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In the user guide, it states the reset is asyn, however, based on the waveform, the reset is de-asserted during the clk_en is asserted.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If further support is needed in this thread, please post a response within 15 days. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page