- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I am using Cyclone V Native Phy for custom protocol.

My simple project using the K28.5 as word aligner symbol.

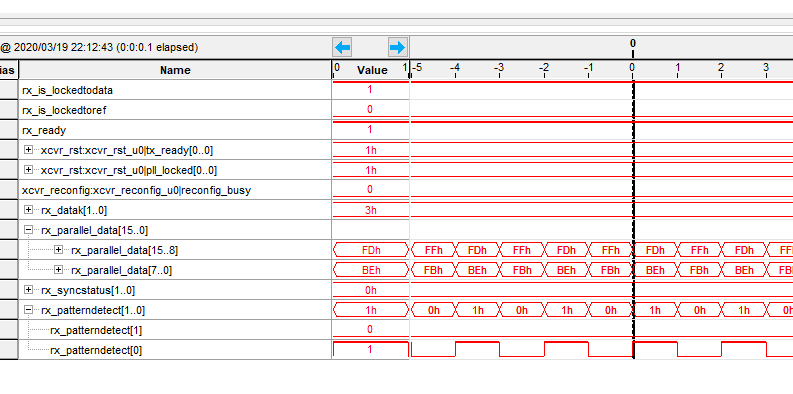

But from signal tap, I see the rx_patterndetect triggered when data is 0xBE instead of 0xBC.

Please see my capture below.

Any idea why the rx_patterndetect asserted at wrong pattern?

Thank you!

BRs,

Johnson

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

As i understand it, you observe in some cases the rx_patterndetect go high even not for 0xBC pattern.

Would you mind to share with me you Native PHY .qsys or .ip file so that I can have a better understanding on your configuration.

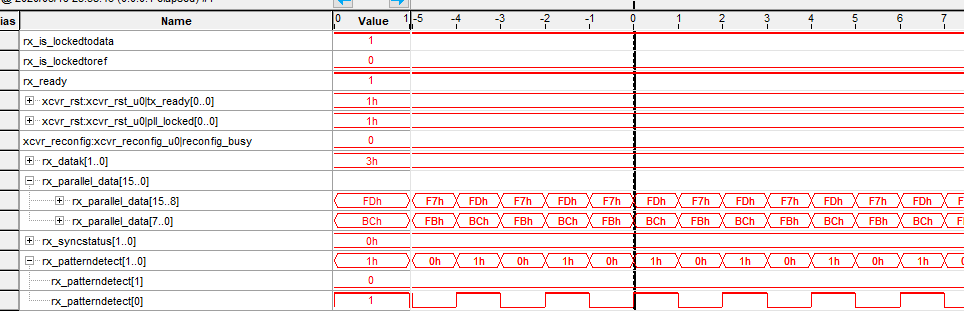

Just would like to check with you also for the 2nd signaltap, do you observe data corrupt? Or if the 0xBE is something expected.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CheePin,

Yes, your understanding is correct that I am expecting to see rx_patterndetect assert for 0xBC.

0XBE is not expected that should not be seen at this stage.

During this stage, only repeated 4-byte idle will be seen.

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

Sorry for any confusion. As I unzip the native_phy that you are attaching, I only observe a native_phy.qip. Would you mind to help sharing with me the native_phy.qsys file?

Regarding the 0xBE, as I understand it, this is not a data that you are sending. Does it mean that the 0xFDBE data pattern is a corrupted data pattern and cause data error at the downstream logic at receiver?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CheePin,

I am using older Quartus Ver.16 for this.

Therefore I did not see the native_phy.qsys in the project.

Would you check the configurations using different file?

0xBE as you understood, is not the data I expected.

Perhaps 0xFDBE is a corrupted pattern, but I don't expect to see rx_patterndetect assetred by this.

BRS,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

Thanks for sharing the file. As I look into the Native PHY .v file, I could not locate any anomaly with it. Would you mind to help performing the following test just to isolate out any potential sampling issue with the signaltap?

1. Can you try to send continous and fixed data pattern ie 0xFDBC to RX to see if it can recover 0xFDBC correctly?

2. In addition, you may try to use PCS-PMA interface width to 20 instead of 10. With this, you will not need to use Byte Ordering and Byte SERDES blocks.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CheePin,

Thanks for the reply.

I did not test again, just to detect the combination of both rx_patterndetect and 0xBC.

Well, it did not trigger for more than 30 mins.

Therefore I suppose it's kind of timing issue related to SignalTap..

Do you think it's possible?

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page