- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I build simulation for the floating IPs, but with modelsim simulation, the outputs are always zero.

I have tried several arithmetic functions, add, sub, accumulate and divide.

However, I got the correct result when simulating the max and min function.

Does anyone know what is wrong with those arithmetic floating IP core?

The IP declaration example

add_sub_fp u0 (

.clk (clk), // input, width = 1, clk.clk

.areset (reset), // input, width = 1, areset.reset

.en (en_feat), // input, width = 1, en.en

.a (data_a), // input, width = 32, a.a

.b (data_b), // input, width = 32, b.b

.q (sum_out), // output, width = 32, q.q

.opSel (sel) // input, width = 1, opSel.opSel

);

Since the quartus updates, they do not provide the previous version of floating IP anymore. This IP core is the only choice to implement floating point function on altera FPGA.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the delay. I was just back to office. As I understand it, you observe some issue with floating point IPs in Modelsim simulation. To facilitate debugging, would you mind to share with me on the following:

- What is the specific Quartus version and IP that you are using?

- Mind sharing with me the .ip file of one of the floating point IP that you are using that I can have better understanding on the configuration.

- Please share with me a simple test design or simulation example which could replicate your observation. I would like to perform issue replication to see if can spot any anomaly.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your reply.

I am using the quartus prime pro 19.2 and the name of the IP core is Floating Point Functions Intel FPGA IP.

I attached the .ip file I am using and as well as the test bench and top-level design wrap.

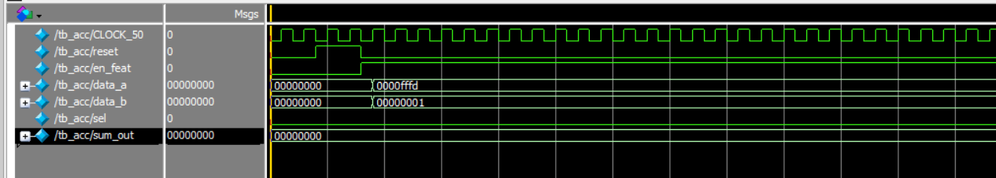

I use a simple add_sub ip as an example, and the simulation results are shown in the below figure.

the result as sum is 0 all the time, I try different value of inputs. No idea on what is wrong with this IP core.

However, I try the max and min function in the same IP core category, which works perfect.

It would be of great help if you could help me to figure out what is wrong with the arithmetic calculation.

Thanks,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. For your information, I have tested with a simple add mode IP in Q19.3Pro and it seems to be simulating correctly. I have sent the zip for your reference through email as it seems like I am unable to attach to the forum. You may run the simulation by doing the following:

1. Change directory to test\test0_tb\test0_tb\sim\mentor

2. Source msim_setup.tcl

3. Type "ld"

4. Type "do wave.do"

5. Type "run -all"

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks Chee pin,

However, I didn't receive your email.

Do you send to the inbox of the forum?

Qian

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Qian,

Sorry for the confusion. As I checked, the file should be sent to your company email. I have sent you the file offline to your company email as well.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page