- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, experts

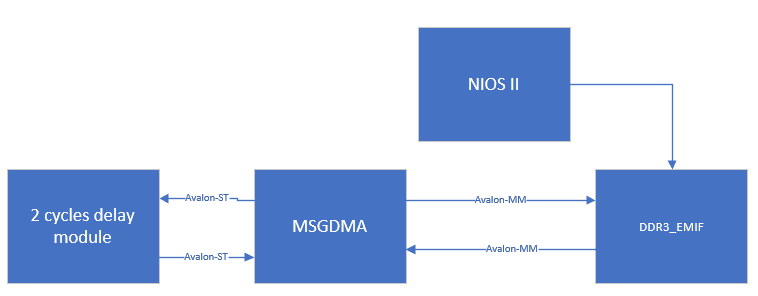

I have built a NIOS II system to verify MSGDMA. The structure is shown as below:

The steps it works:

- NIOS write test pattern to some certain space in DDR3

- NIOS configure MSGDMA to mm2mm mode

- Write descriptors to MSGDMA and the Read Master read test pattern out and send to the 2-cycle delay module

- Write Master send the data back to DDR3, but at different memory space.

- NIOS read the data out and compare with the original test pattern.

When it begins to run, the system always hang on waiting for completion IRQ, but no IRQ generated. I checked the memory, some data were lost during transfer.

When I remove the delay module, and directly loopback the Avalon-S T port of Write Master and Read Master, everything goes well.

My question is , is it possible to add some processing module when MSGDMA in MM2MM mode ? if yes, How it handle it ?

Link Copied

1 Reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I come back to finish this , I solved this in a very simple way, that is , set the msgdma data fifo depth larger !

Reply

Topic Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page