- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi Sir,

How to read frame buffer contents?

I have to read the frame and process it and write the processed frame to frame buffer again in NIOS2 ECLLIPSE .

where can i get the brief description for VIP based nios2 functions and parameters?

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Did you check the available examples for VIP on our design store? Please check the following and let me know if this was useful for you.

https://fpgacloud.intel.com/devstore/?search=VIP

Regards,

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Where you store this frame buffer? On-chip memory or external RAM?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

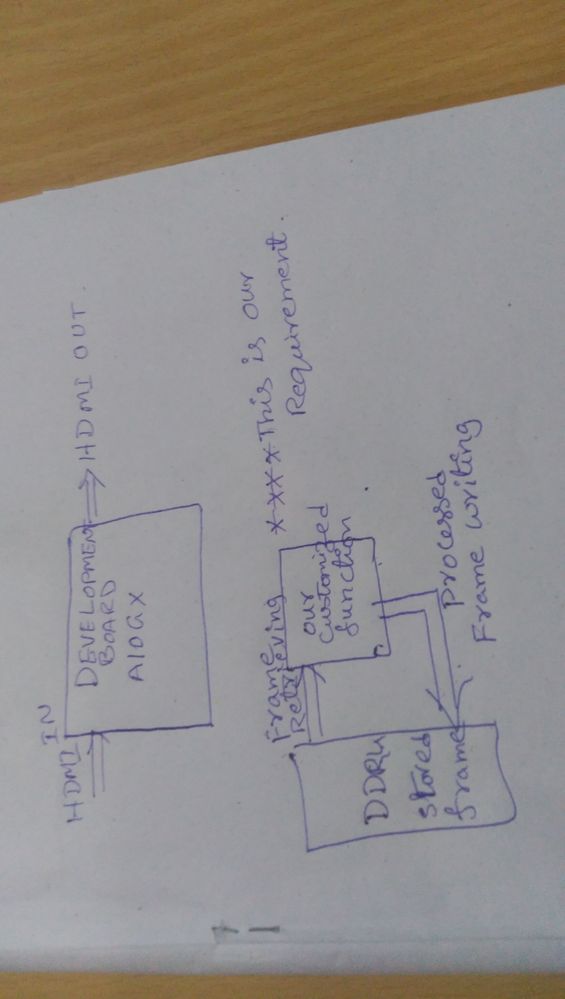

Please see the attached functional diagram.It is our requirement.

Please provide your guidance for the following required functional implementation.

1. Frame Buffer Accessing in the VIP Control Source code for implementation of our customized conversion.

2. Brief description for VIP based nios2 functions and passing parameters.

Functionalities to be implemented in the FPGA:

1. Display Data receiving from HDMI Receiver.

2. Stored Frame content from DDR4 sdram to be retrieved.

3. Implementation of customized conversion process.

4.Storage of conversion data to DDR4 sdram.

5. Sending converted video data to HDMI Transmitter.

Pls guide me .

Thanks and regrds

D.SUVARNA