- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are now having our students buy the DE10-Lite boards for a sophomore digital design course. About a quarter of the students go on to take an advanced digital design course and have need to use the on-board SDRAM for that course. I've been hesitant to install newer versions of Quartus due to the SDRAM controller going away. Is there a suitable replacement for the educational boards?

The reason we use Intel Quartus rather than Xilinx is so the students can run free versions of the software on their own computers and not need to physically be in our labs to work on these projects. I'm therefore looking for something that can be used with the lite/web versions of the software. Being able to play with the parameters (latency, etc) would be ideal for this advanced class, but we would settle for just having the ability to use the components on the educational board.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm not sure what you mean by "the SDRAM controller going away" in newer versions of Quartus. There should be no issues with using those boards in newer versions of the software.

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

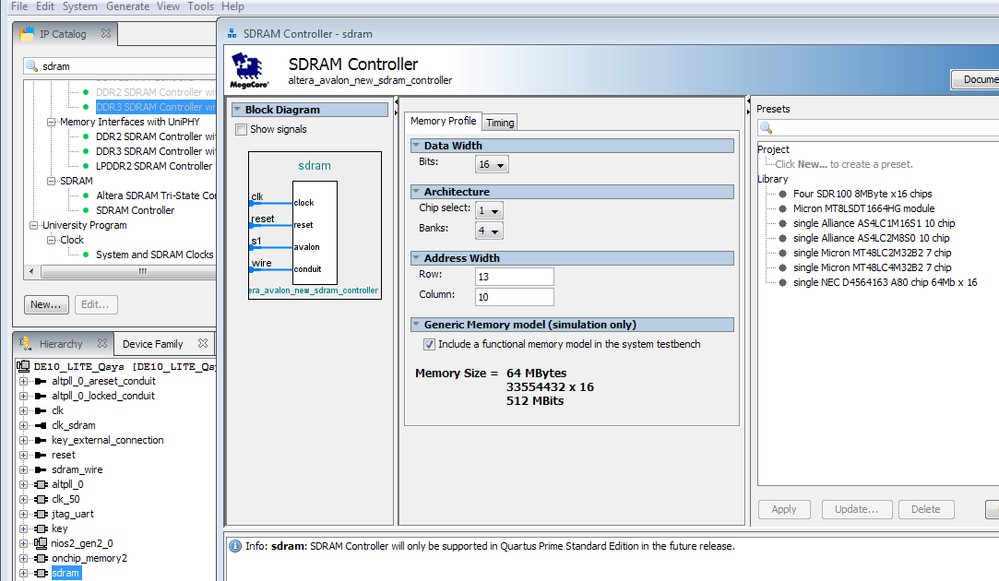

Intel has indicated that the Qsys component for the SDRAM controller will no longer be available for use with the free software after Quartus V16.1. If you try to instantiate a SDRAM controller (using Qsys) in 16.1 it warns of this in the comment box for the component. I have not installed Quartus 18, but have looked at an install and did not see the SDRAM controller. Have I been mis-informed?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

For information , if your still use DE10-Standard (Cyclone V SoC dev board from Terrasic) as I do for a quick proof of concept design,

While recompiling old demo projects from Terasic for DE10-Standard, and in particular the SDRAM_Nios_Test as archived in the CD_DE10 (at this time generated under V16.1), confirm with Quartus prime lite V21, the legacy SDRAM controller generates an error, in revange with a fresh install of Quartus Prime Lite Version 17.1.0 Build 590, (downloaded April 2025) the QSys module still displayes as upgraded from 16.1 to 17., the initial SDRAM Controller: named "altera _avalon_new_sdram_controller " Version 17.1 and compilation is successfull with 0 Error.

Best Regards.

Fred

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You are correct. But now you would use one of the UniPHY based IPs instead of the old SDRAM controller IP. They're even listed there in the screenshot you posted. Start here for information on EMIF solutions and documentation:

https://www.intel.com/content/www/us/en/programmable/support/literature/lit-external-memory-interface.html

The Design Guidelines handbook shows you how to add and parameterize the newer IP:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/external-memory/emi_plan.pdf

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

@sstrelldiscussed SDRAM is single-data-rate DRAM, UniPHY and above linked EMIF solutions are exclusively supporting DDR RAM.

I checked SDRAM IP available with several Quartus versions. sopc_builder_ip/altera_avalon_new_sdram_controller is still shipped with Quartus V19.1, Lite and Standard. It's no longer available with V21 and later. DE10_Lite SDRAM_Nios_Test can be used as is up to V19.1 but not with newer Quartus versions. DE10_Lite SDRAM_RTL_Test works up to latest Quartus 24.1. Means the problem isn't SDRAM controller, only Avalon interface is missing.

To use DE10 SDRAM with newer Quartus versions, you have two options.

1. Use available SDRAM controller HDL, e.g. SDRAM_RTL_Test and design Avalon interface yourself

2. Copy Quartus V19.1 IP to your Quartus version, I tried succesful with V22.1. You need to copy ip/altera/sopc_builder_ip/altera_avalon_new_sdram_controller folder and the related entry in altera_components.ipx

Most recent Quartus versions (e.g. V24.1) also dropped Nios II IP, presume you want to stay with Nios II and previous Quartus version.

Regards

Frank

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page