- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Hi,

i try to implement a SPI-to-Avalon-Master-Bridge together with an On-Chip-Flash on a MAX10. I connected both in QSYS and started a simulation. Unfortunately the Bridge always answers with "IDLE" (0x4A). By using the Intel documents I searched out the following bytes in order to read status register (address 0x0000_0000) of the On-Chip-Flash:

0x7A, 0x7C, 0x00, 0x10, 0x00, 0x00, 0x04, 0x00, 0x00, 0x00, 0x7B, 0x00

Do I have to start transmitting with 0x7A (from left to right)? --> 01111010 (from left to right)

Can nss be low during the complete transaction or has nss to be deactivated after each byte?

Is there something else, I have to watch out?

Thank you.

- Etiquetas:

- avalon

- MAX10

- on-chip-flash

- qsys

- SPI

Enlace copiado

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

You may checkout the section 4. Avalon-ST Serial Peripheral Interface Core.

The Avalon-ST SPI core waits for the nSS signal to be asserted low, signifying that the SPI master is initiating a transaction. The core then starts shifting in bits from the input signal mosi.

Thus, the nss need to be low during the complete transaction.

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Hi,

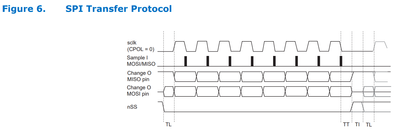

I already found section 4 and figure 6 in the documents, but figure 6 only shows a transaction including 1 byte. I don't know exactly how to write a complete transaction. What byte and what bit has to be sent first? I want to simulate a read operation at avalon adress 0x0000 0000 (that should be status register of the On-Chip-Flash) with Modelsim. After reading the documents, I think I have to sent the following bytes:

0x7A, 0x7C, 0x00, 0x10, 0x00, 0x00, 0x04, 0x00, 0x00, 0x00, 0x7B, 0x00

But the IP Core always answers with IDLE (that means that there is no data to send).

Could you help me modifying my modelsim script attached in order to run my read operation?

Thank you.

- Marcar como nuevo

- Favorito

- Suscribir

- Silenciar

- Suscribirse a un feed RSS

- Resaltar

- Imprimir

- Informe de contenido inapropiado

Hi @Jo910

Sorry for the late reply. Do you need further help regards to this case?

I do not think I can get any useful information from the attachment.

You may checkout the design example here for reference.

Best Regards,

Richard Tan

p/s: If any answer from the community or Intel support are helpful, please feel free to give Kudos.

- Suscribirse a un feed RSS

- Marcar tema como nuevo

- Marcar tema como leído

- Flotar este Tema para el usuario actual

- Favorito

- Suscribir

- Página de impresión sencilla