- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

To be able to test our FPGA-Design in total, I’d like to connect a flash model of the S25FL128S with the ASMI Parallel II Core. I’m using a Cyclone V, and Quartus Version 18.1 Lite.

As far as I understand it, I’m supposed to write a wrapper that connects the block dut_asmiblock from altera_asmi2_qspi_interface_asmiblock.sv with the top-level block of the flash. However, regardless how I try to connect these two, I only manage to read ‘Z’. The AN-720 states that I should connect to the asmi_sim_model, not this block, but asmi_sim_model is not existing in the simulation folder of the ASMI Parallel II block. Do you have any hint for me what I am doing wrong here?

dut_asmiblock instance:

cyclonev_asmiblock dut_asmiblock (

.dclk(atom_ports_dclk),

.sce(atom_ports_ncs),

.oe(atom_ports_oe),

.data0out(atom_ports_dataout[0]),

.data1out(atom_ports_dataout[1]),

.data2out(atom_ports_dataout[2]),

.data3out(atom_ports_dataout[3]),

.data0oe(atom_ports_dataoe[0]),

.data1oe(atom_ports_dataoe[1]),

.data2oe(atom_ports_dataoe[2]),

.data3oe(atom_ports_dataoe[3]),

.data0in(atom_ports_datain[0]),

.data1in(atom_ports_datain[1]),

.data2in(atom_ports_datain[2]),

.data3in(atom_ports_datain[3]));

defparam

dut_asmiblock.enable_sim = ENABLE_SIM_MODEL;

ports of the flash block:

PORT (

-- Data Inputs/Outputs

SI : INOUT std_ulogic := 'U'; -- serial data input/IO0

SO : INOUT std_ulogic := 'U'; -- serial data output/IO1

-- Controls

SCK : IN std_ulogic := 'U'; -- serial clock input

CSNeg : IN std_ulogic := 'U'; -- chip select input

RSTNeg : IN std_ulogic := 'U'; -- hardware reset pin

WPNeg : INOUT std_ulogic := 'U'; -- write protect input/IO2

HOLDNeg : INOUT std_ulogic := 'U' -- hold input/IO3

);

Best regards,

Nanuq

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

First of all, i think ASMI Parallel II IP is only supporting EPCQ, EPCQ-L, and EPCQ-A devices. If you are using third-party flash devices, you must use the Generic Serial Flash Interface Intel FPGA IP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi

Thanks for your answer. On the actual board I'm using the EPCQ-A device. But I'd like to simulate my code first. The point is: the ASMI Parallel II datasheet writes the following:

Uses the default EPCQ 1024 simulation model for simulation. If you are using a third-party flash device, refer to AN 720: Simulating the ASMI Block in Your Design to create a wrapper to connect the flash model with the ASMI Block.

I'd love to use the default simulation model of EPCQ 1024, but it does not seem to be included in the ASMI parallel II simulation model of Quartus 18.1 either. When I try to simulate without the third-party flash model and enable_sim set to TRUE, Modelsim is not capable of finding a valid cyclonev_asmiblock.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Before that, just want to check with your steps in setting up the simulation. Have you included the testbench and its setting before the compilation? You may refer to the link below for the steps.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_gs_msa_qii.pdf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I have included the testbench, and set the settings before compilation.

I am able to follow the signals in simulation through the files, from asmi_parallel.vhd to the submodules asmi_parallel_asmi_parallel2_top_0.vhd, asmi_parallel_asmi_parallel2_top_0_asmi2_core.vhd and altera_asmi2_qspi_interface.sv to the altera_asmi2_qspi_interface_asmiblock.sv (all of them compiled and simulated fine).

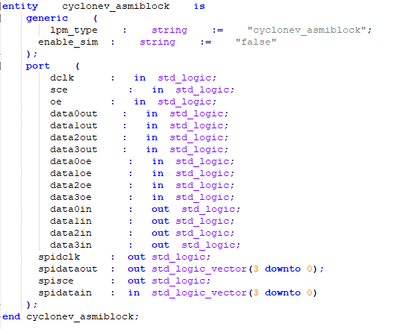

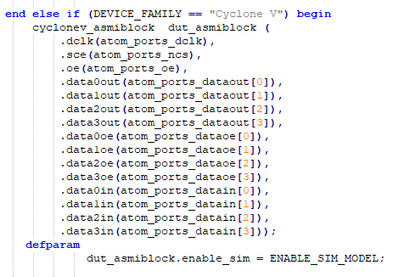

In the altera_asmi2_qspi_interface_asmiblock.sv, the cyclonev_asmiblock then cannot be found by the ModelSim. I did include the library "altera", but there, the only thing I can find (humanly readable) is the cyclonev_asmiblock_info.xml, and the ports defined there do not match the ports defined in the altera_asmi2_qspi_interface_asmiblock.sv, the SPI signals spidatain, spisce, spidclk and spidataout are missing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I was trying to duplicate your issue but no luck with it. Can you share me your testbench file?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I attached the relevant files to this reply. I want to point out, none of the added files are written by me, some are generated by the IP Parameter Editor / IP Catalog, the cyclone V ones are installed when installing Quartus 18.1.

I still think that the problem is, that the entities of the ASMI Parallel II asmiblock and the Cyclone V asmiblock do not match.

But anyway, I decided to not simulate the ASMI Parallel II block but to access directly the Avalon bus, so I'm not working with this anymore.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page