- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am working on a simple project that with CVI/ PTG -> Switch -> CVO -> HDMI at 1080p.

Sometimes the CVO is not outputting any signal from PTG.

From Signal Tap, I noticed for CVO or Switch the ready signal is not set after boot and reset.

What cause this issue?

Or how could i debug?

Thank you!

BRs,

Johnson

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

When you say "Sometimes the CVO is not outputting..." - does it ever output anything from the PTG?

Is your software setting the switch up correctly to select between the CVI/PTG? The switch's control register expects a one-hot value to select the required input.

Are you getting any output from the CVO btw?

Regards,

K

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

If I understand it correctly, when you are referring to the ready signal of Switch II is not asserted, I believe you are referring to the din_<>_ready output ports.

If yes, for your information, K is correct. After power up, you will need to write to the Control register to start the Switch II.

As for the CVO, if you enable the control ports, then you will need to write to its register to start it as well.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi K and Chee Pin,

Thank you for the reply.

I think I am looking for why the Switch II IP is not responding to new configuration.

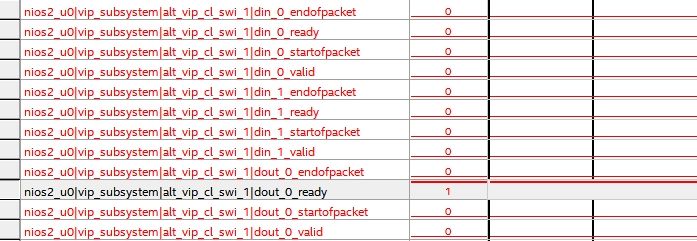

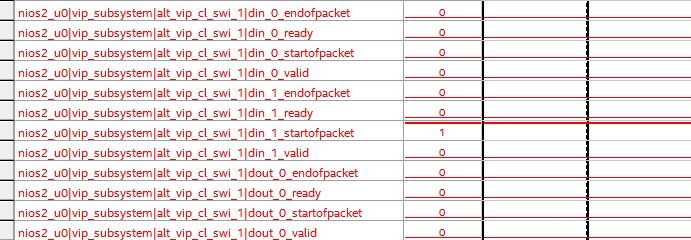

Below are signals from my project.

din_0 is PTG

din_1 is CVI

dout_0 is frame buffer and will output to CVO.

After download and before any config, the ready signal raised.

CVI is Go but without any valid input data.

And PTG is "Go" at 1080p RGB 10 bit.

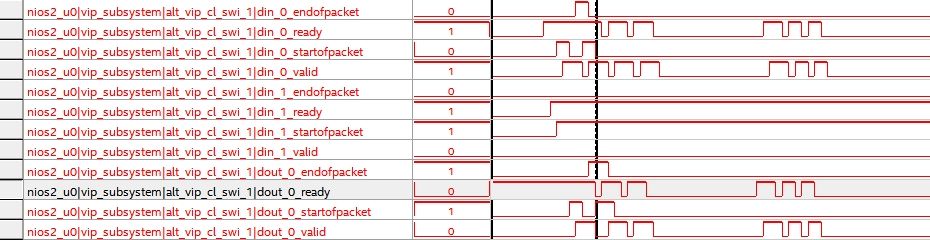

After programming registers to .Dout_0 from din_0 and both inputs as consume mode.

After config,

Then I download the nios ii again to do new configuration.

The Status value of Switch kept at 1.

I tried using 2 different ways to update the new values but the IP is not responding.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your update. Would you mind to further elaborate on what is the new configuration that you have loaded to the Switch? Please share with us the detailed steps ie the register and values that you are writing to configure the Switch to see if we can spot any anomaly? Also, mind share more on the 2 different ways that you mentioned tested?

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

By the way, to ease the debugging, probably you can use two TPG with different video patterns since there is no valid video input to the CVI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CP,

Here's the configuration and steps,

- Set CVO to "GO" and clear underflow.

- Set CVI to "GO"

- Config PTG as 1080p then "GO"

- Config Switch, input source from PTG. din_0 and din_1 as consume mode

- Write Switch address 0 to 0, stop the switch.

- Keep reading Switch Status till it's 0.

- Set Swithc to Go.

Here's the result,

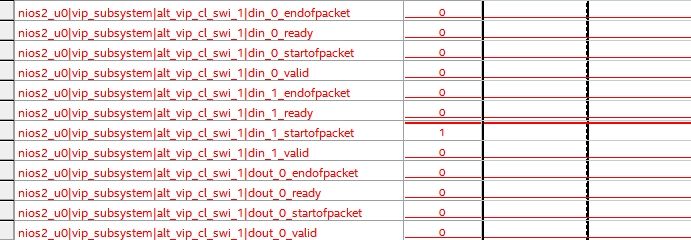

Download Nios and repeat above procedures,

At Step 6, Nios kept reporting Status as 1. And not response to any configuration.

Captured Signals like below,

And thanks for the suggestion,

I am working on a new VIP, with 2 switches and 2 PTGs.

CVI and PTG_0 go to Switch_0. Switch_0 out to frame buffer.

FB and PTG_1 go to Switch_1. Output of Switch_1 to CVO.

PTGs are of different pattern.

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CheePin,

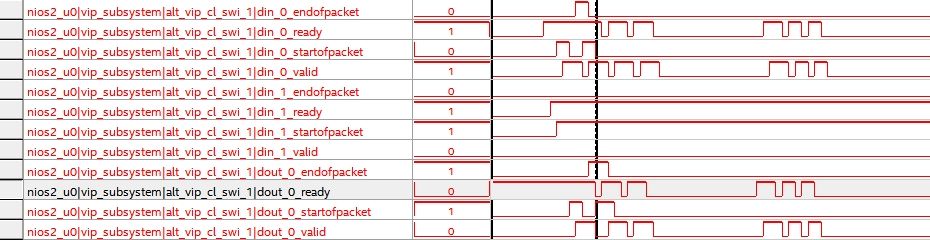

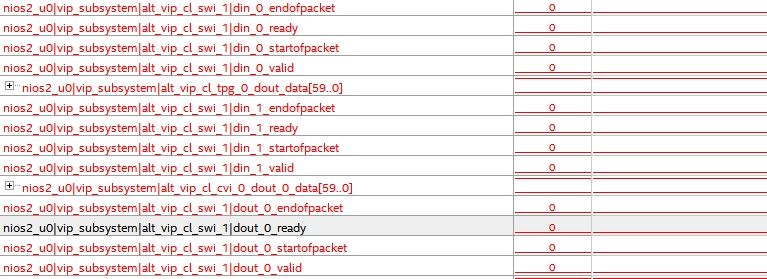

The new configuration shown similar problem, when I catch signals like below.

Firmware always returns Status as 1, updating to Switch is not applicable.

dout_0_ready came from frame buffer, it switched to low when switch is "GO".

Any comments?

Regards.

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Chee Pin,

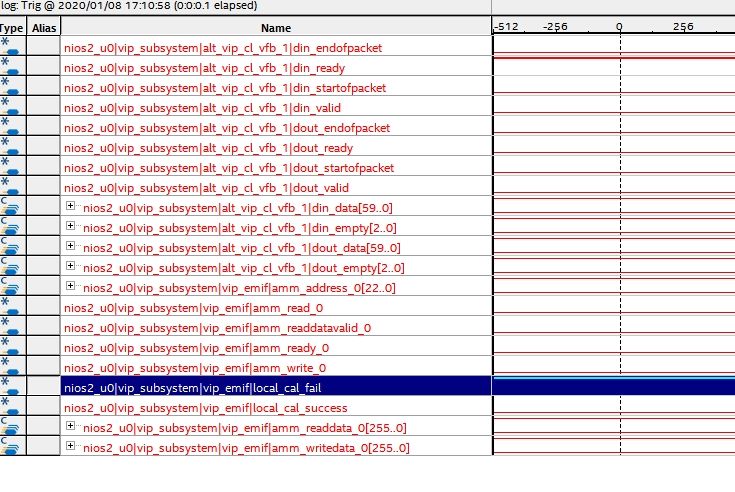

I think the problem is the memory controller.

I find the frame buffer ready signal was gone after "GO" for a short period.

Then I get the memory signal and noticed that the local_cal_fail raised.

This explains why the frame buffer will turn to not ready when switch is "GO".

Any suggestion on how could I debug this?

Please comment.

Thank you!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

thanks for your update. To further isolate this, can you try to create a simple test design without the frame buffer and external memory. For example, 2 TPGs -> Switch -< CVO. Then try to see if after switching, there is any anomaly with the switch. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CP,

Sure, I will.

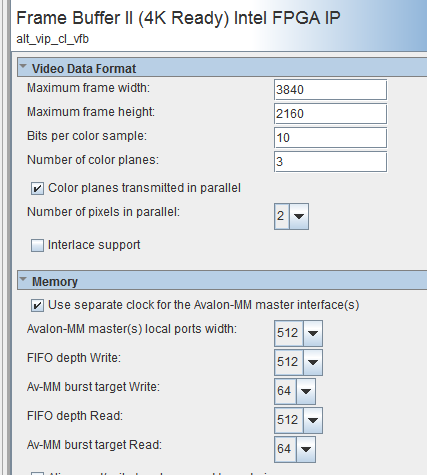

By the way, I have a question on Cyclone 10 vip reference,

As the memory controller runs at Quarter mode with 32-bit width, why the frame buffer configured to 512-bit width?

Can you help check this?

Thank you!

BRs,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi CP,

I would like to continue the discussion on Mixer.

Mixer core stopped for unknown reason after I config the Input Control to enable.

This time the source of mixer input 0 coming from frame buffer and input of frame buffer is PTG.

output of mixer connect to a chroma resampler then CVO.

Mixer was configured with YCbCr 422 with Alpha Blending Enable, banckground is uniform.

When I set mixer to consume mode, the ready signal is always fine.

But when I switched to Enable, it stopped.

I attached the compressed stp file for your check.

As you can see, mixer received control packet at time 0 as 1920x1080p.

As soon as mixer received video packet at time 144 with 2 valid pixels.

Then ready signal switch to low.

Although the ready signal for CRS and CVO are always fine.

Any idea why this happened?

Regards,

Johnson

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for the late response. Regarding your latest inquiry on the HDMI example design, please allow me sometime to further consult HDMI IP folk to see if they are aware of the reason behind. I do not have much visibility into this example design. Please ping me if you do not hear back from me by early next week.

By the way, just wonder if you observe any issue with the issue with 512 bit width?

Please let me know if there is any concern. thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

Regarding your latest inquiry on the frame buffer width + memory controller for the HDMI example design, as per my discussion with the HDMI and memory folks, they would like to recommend you to open a new case so that they can further look into. Please feel free to let me know the case number after you open it to facilitate the routing.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Johnson,

As I understand it, your latest inquiry is related to Mixer. I have tried to look into the signaltap but sorry as I could not really tell what might be wrong based on it.

To facilitate further debugging, would you mind to help creating a simple test design with minimal instances ie TPG -> Frame buffer -> Mixer and run through simulation to see if can replicate similar observation? This will be helpful to isolate any functional issue prior to hardware debugging. To facilitate the test, you can set the video size to low ie 100x100 so that you can make use of on-chip memory for the frame buffer. This will also help isolate external memory from the debugging.

Please let me know if there is any concern. Thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page