- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi all,

we met a performance issue on Arria10 mSGDMA Avalon-MM master(32bit data width) interconnect to PCIE HIP's Avalon-MM (w/ DMA) slave (txs 32bit).

For "mSGDMA_writing_to PCIE AVMM(w/ DMA) TXS" operation, data transfer performance is good.

But for revere "mSGDMA_reading_from PCIE AVMM(w/ DMA) TXS" direction, data transfer is very slow, we monitored the "txs waitrequest" signal to de-asserted to activate , found found the reading consumes much more clock cycles (16 x) than writing operation. This blocks us for a long time yet.

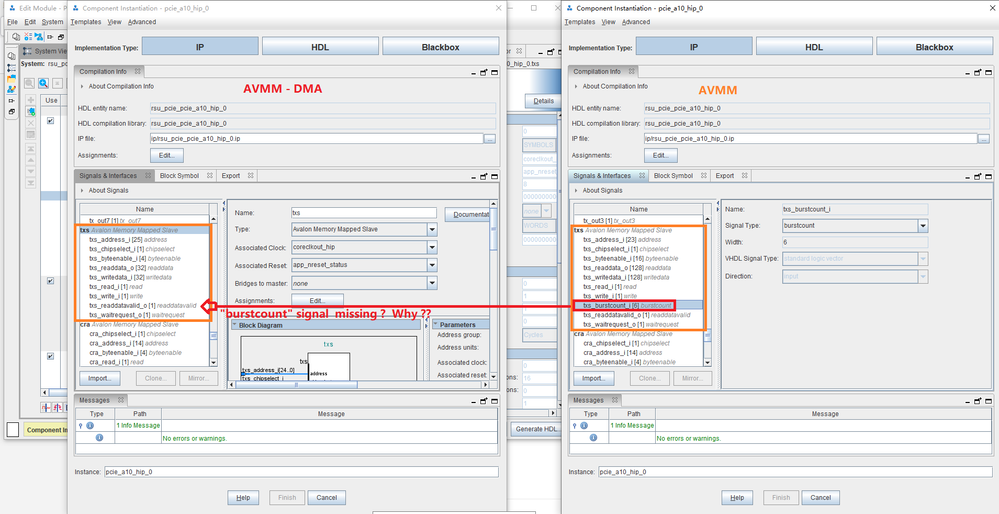

I just compare Avalon-MM interface signals between PCIE HIP's "AVMM ( with DMA)" vs PCIE HIP's "AVMM" variant, then we found the "txs burstcount" signal is missing in PCIE HIP's "AVMM ( with DMA)" interface , while it really exist in PCIE HIP's "AVMM" interface, as following pic:

so my question is : waht's the reason of this difference ? Does this "txs burstcount" miss in AVMM-DMA interface would affect the reading (burst) opearion from mSGDMA AValon-MM Master to PCIE HIP TXS (avalon-mm slave) ?

Appreciate helps & advices if any. Thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

pls kindly reply

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page