- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

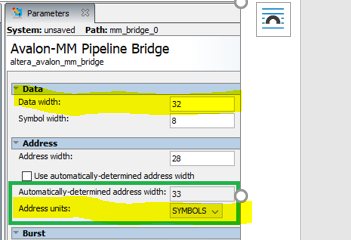

I have a Platform Designer design with two DDR3 memory controllers. They both require 28-bits address on the Avalon bus. I want them to look like contiguous memory. I want to connect an Avalon-MM Pipeline Bridge to connect them. The slave port on the bridge should be 29 bits with the high bit representing the switch between the two memory controllers. I configured each memory as 8GB (1Gx64) SODIMM configuration with row/column/bank equal to 16/10/3 bits. The memory controller suggests that I only need 28 bits of Avalon address. However, when I go through the Avalon-MM Pipeline Bridge component it adds 5 address bits on top of that. Can you tell me why? Can you suggest a better way to set up the memories so they look like one big memory? I could write the controller myself but was hoping Intel had IP to take care of it.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

Welcome to Intel Community.

As I can see the data width from DDR3 controllers and bridge is difference.

You can change the data width to be the same, and then address unit changed to "words".

Meaning, change the bridge data width from 32 bits to 256bits. Then, change the address unit to "words".

Thanks

Regards,

Aida

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page