- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm running Quartus 18.1.2 with Stratix10 GX Devkit board.

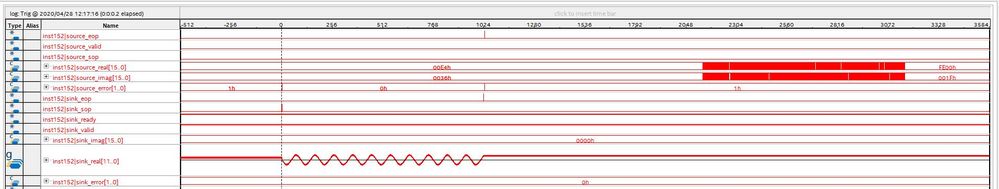

Here is attached picture of signal tap logic analyzer showing the proper sink_sop/eop/valid. It is strange that FFT still outputs data even without source_sop/eop/valid. Anyone seen this behavior?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for any confusion. To ensure we are on the same page, would you mind to further elaborate on the issue observation. Probably some screenshot with markings of places with anomaly would be helpful.

As I look into your signaltap, seems like the source_error seems to be asserted when there are toggling at the source_real/imag. Also, the source_valid seems to be de-asserted during this period. Without the valid, the source_real/imag signals are invalid and can be ignored.

I believe you mignt need to further look into why there is no valid out from the FFT. It is recommended for you to perform a functional simulation to see if you can replicate similar observation. You can then further debug from there to see if can spot any anomaly.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page