- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

So, I have created a PLL with a 50MHz clk in.

From there I generate two clocks. C0 = 100MHz, and C1 is 100KHz.

The PLL achieves these values by having an M = 12, N=1 and a C0 counter of 6 for the 100MHz clock.

However for C1 it use post counter of 500 but also a cascade tap of 12 to get the 100KHz.

All good as far as I am concerned and I generate the mif file for use in the PLL reconfig IP.

So when I fire up the PLL out of reset all is good, C0 = 100MHz and C1 = 100KHz.

However if I reconfigure the PLL using the reconfig IP that has been setup using the generated mif, then C1= 1.2MHz, in other words it stops using the cascade tap for C1.

The same is true if I try to change the post scale counter for C1 and then change it back to its original setting.

How can I prevent this from happening? There does not seem to be a way to setup the use of cascade tap using the 144bit scan chain????

please help

- Tags:

- pll

Link kopiert

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

I can't explain why this is happening. However, I can offer some thoughts.

Which device are you using? I'm surprised Quartus allows you to specify a clock out of 100kHz. Outputs are often restricted to something over 1MHz. However, it clearly works. My suspicion is that the cascade simply cannot be reconfigured and you're ending up with the lowest frequency that the PLL can generate.

Regardless of this I'd highly recommend not designing in this way. Operate your logic at a higher frequency and have a 100kHz 'tick' within your logic indicating when to run the circuitry that needs to operate at 100kHz. If you need a true, 50/50 mark/space ratio output signal, generate this in logic as well.

If, by reconfiguring your PLL, you need to move away from 100kHz, then adapt your logic as appropriate.

Cheers,

Alex

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

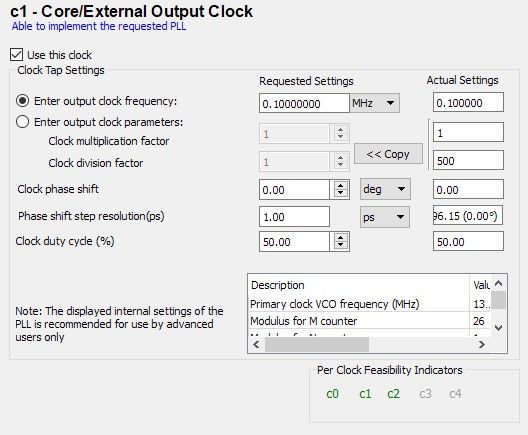

Here is the config wizard stating that 0.1MHz is achievable: I have synthesized and implemeted this on the HW.

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hi Gentlemen,

I am using the MAX10 10M08SA I use the ALTTPLL IP in quartus prime (18.xx), I set up clkin at 50MHz, and then C0 I set to 100MHz. I then set up C1 and C2 to be 0.1MHz and it works fine. I actually do something a bit naughty after this and phase shift C1, then XOR the together to get very narrow pulses at twice the freq, but that is an aside. I have proven that I can do this physically using an eval board, but I havent proved physically that I can also do this once I use the reconfig IP. The physical test was done with the ALTPLL config fixed and no reconfig options enabled.

ddB

- Als neu kennzeichnen

- Lesezeichen

- Abonnieren

- Stummschalten

- RSS-Feed abonnieren

- Kennzeichnen

- Anstößigen Inhalt melden

Hello , Ah you are using max 10 . Yeah I agree Post scale counter cascading not possible as per user guide.Here is the link below ,Refer page 31/67.

Thank you ,

Regards,

Sree

- RSS-Feed abonnieren

- Thema als neu kennzeichnen

- Thema als gelesen kennzeichnen

- Diesen Thema für aktuellen Benutzer floaten

- Lesezeichen

- Abonnieren

- Drucker-Anzeigeseite