- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

How to make sure data is aligned with fclk when using altlvds_rx ip?

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

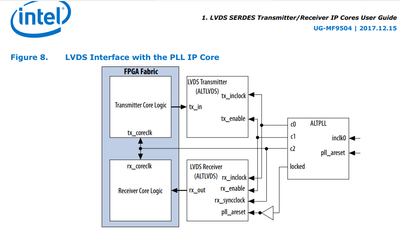

Please refer the ALTLVDS user guide section 1.3.2: https://www.intel.com/content/www/us/en/docs/programmable/683062/17-1/lvds-serdes-transmitter-receiver-ip-36681.html

In external PLL mode rx_coreclock can be used in the fabric logic to further process the data. In this mode, rx_coreclock is same as the rx_syncclock which is an input to the ALTLVDS_RX.

rx_syncclock is used to receive the parallel data.

Regards

コピーされたリンク

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Can you please tell which device IP are you using?

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

The ALTLVDS IP has rx_coreclock signal. You can connect the fabric clock to it.

Regards

- 新着としてマーク

- ブックマーク

- 購読

- ミュート

- RSS フィードを購読する

- ハイライト

- 印刷

- 不適切なコンテンツを報告

Hi,

Please refer the ALTLVDS user guide section 1.3.2: https://www.intel.com/content/www/us/en/docs/programmable/683062/17-1/lvds-serdes-transmitter-receiver-ip-36681.html

In external PLL mode rx_coreclock can be used in the fabric logic to further process the data. In this mode, rx_coreclock is same as the rx_syncclock which is an input to the ALTLVDS_RX.

rx_syncclock is used to receive the parallel data.

Regards