- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi

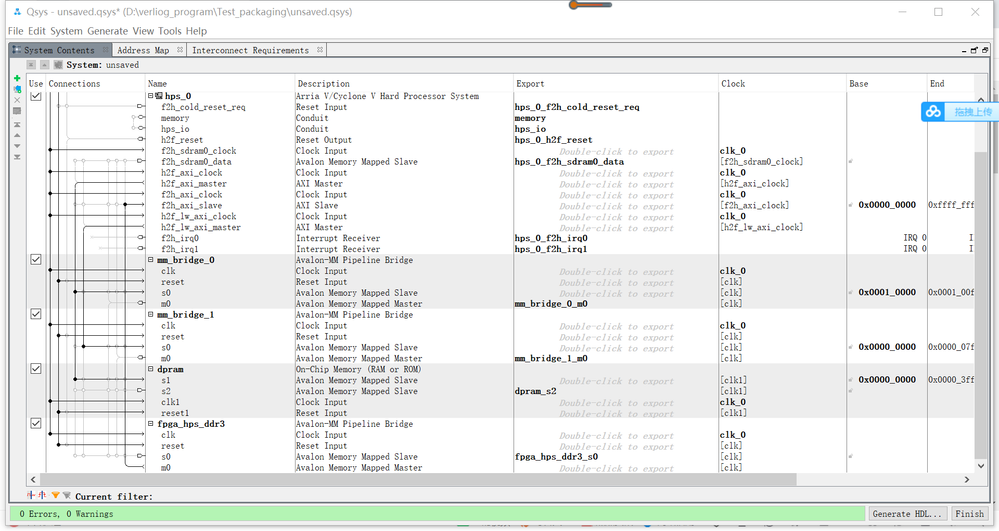

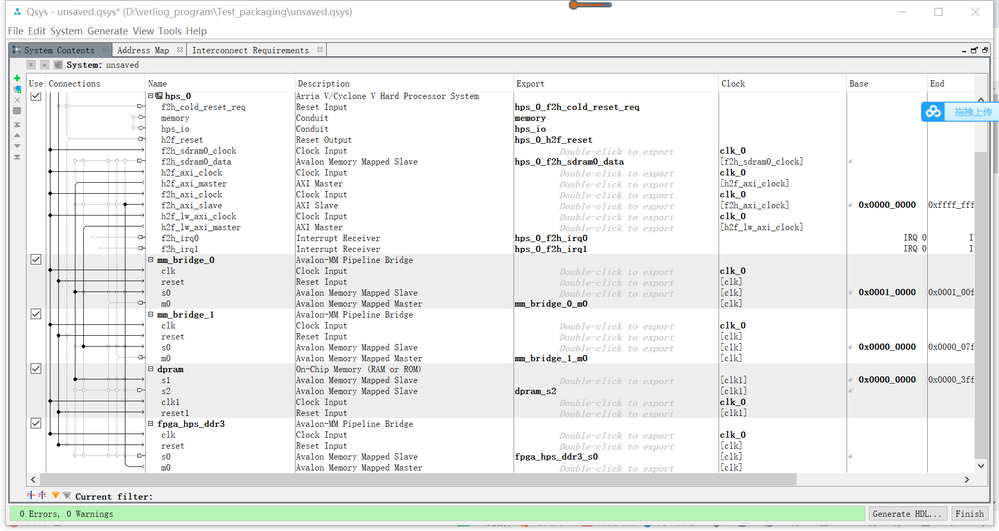

In HPS, I connect an Avalon-mm-bridge host to f2h-Axi-slave, and export the slave of Avalon-mm bridge from the machine. Can I read and write DDR3 on the HPS side directly?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, FPGA1.

Thank you for posting in the Intel Community Support forum.

I will route your thread to a section for similar issues/questions so it can get answered as soon as possible.

Best regards,

Bruce C.

Intel Customer Support Technician

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It is recommended that you do all interconnect and bring it inside Platform Designer than exporting it out. If you are trying to access the DDR3 of the HPS , you will need a EMIF IP for the HPS and set the settings a per spec of your DDR connect it to the HPS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Any followup from your side?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry, I just logged in today

I'm a little bit delayed now. I didn't continue with it

But I want to ask, can't Avalon mm bridge be imported from SoC system as data input on FPGA side? I just searched the EMIF IP, but I didn't find it. Can I explain this in detail

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I just went to cut a picture for you,We are eager to solve this problem ,thanks

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page