- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I have a requirement to route the I2C(master) in HPS to FPGA and connect the I2C signals to an I2C slave IP(IO Expander logic).I tried to in the following way

under parameter(hard processing system intel arria10 FPGA IP-->Pin Mux and peripherals-->Advanced FPGA placement(under route to FPGA I changed the dropdown corresponding to I2C0 as Yes)

I am a bit doubtful about the I2C IP configuration, SCL signal is declared as input in the HPS signal list in platform designer system content tab.

is it possible to configure the I2C in HPS as master and route it to FPGA?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The I2C is a peripheral of the HPS. As such, it's accessed by the FPGA over the bridges between the two halves of the device (h2f, f2h), typically through the address map of the HPS.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

thanks for the reply sstrell,

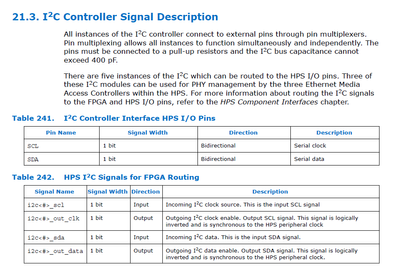

I am checking the possibility of the I2C which is explained in 4038 of Intel® Arria 10® Hard Processor

System Technical Reference Manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Nithin,

First of all, thank you for reaching us.

Regarding your issue... yes it is possible to configure the I2C in HPS as master and route it to FPGA, to do this please take a look into the next documentation, page #11, you will find a couple of lines for instantiation, you will need to copy them and add them to your *.v file

Regards,

-Eliath

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello,

Thankyou Eliath for your reply

i understand the ALT_IOBUF Primitive instantiation.

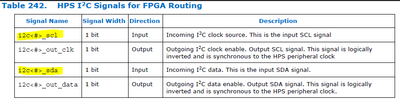

In the attachment, I have highlighted the pins of I2C which will be visible to FPGA and that looks like slave .

for example: what I understand is SCL is an Input port which means the clock will come in from the master, so it is a slave.

please correct me if i am wrong.

Regards

Matt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Nithin,

Yes, SCL is provided by the master.

SCL is not only the clock, it is also used to receive the acknowledge signal from the slave.

Regards,

-Eliath Guzman

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello Eilath,

yes the clock should be supplied from the master,

here is my point ,when we route the I2C from HPS to FPGA we have the following signals available

since SCL signal is specified as input , then it can only receive the clock, it cannot drive any clock!!

So what I understand from the port list is that, the IP is a slave.

I am looking for the Master I2C from HPS ,accessible to FPGA to connect to a slave in FPGA.

*I think, SDA signal receive the acknowledge signal from the slave, not the scl.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page