- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

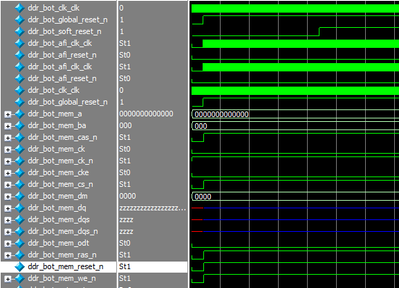

i have ArriaV, DDR3 chips, but after deassert global and soft resets mem_reset_n stay is low. Soft reset generate after 1000 tick on 100MHz clk

What else can affect this signal?

- Tags:

- controller

- ddr3

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Sir,

I'm Adzim. Thanks for using Intel Community.

According to the KDB here, it's looks like the global and soft resets can only trigger the mem_reset_n signal.

Are you using the example design in your simulation?

If not, can you simulate your IP with the example design?

Which Quartus software that you used?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you try to simulate your IP with the example design in your simulation?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

At the moment, no, since there were no problems when using the core on Cyclone 5

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Can you give it a test?

So before this you're working on Cyclone V device and it's worked.

But now you try to implemented it in Arria V is it?

Do you create a new IP for the Arria V or you use the existing project?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I copy qsys file with DDR3 controller from CycloneV project to ArriaV project, ofcourse i change FPGA type in qsys file

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for clarifying about your project.

I guess there is no error during the IP generating process and compilation.

But since you're facing some issue with the Arria V device, can you use the example design to simulate your IP in the Arria V?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I try to simulate... and all signals correct

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Great!

Can you check the connection between your IP and your design?

And compare it with the example design.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I create new project with same qsys file with ddr3 controller

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I changed the core type to soft controller and keep track of mem_reset_n generation.

dataout[0] from ARRIAV_DDIO_OUT - mem_reset_n

pll_addr_cmd_clk - exist

DATAINHI and DATAINLO - 2'b11

ARESET - 1'b0(from ~reset_reg[14])

Why???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sir,

The signal tap tool cannot be used to get the signal from the mem_reset_n because the signal is the conduit between the memory and phy.

The signal tap can get the signal between user design and the memory controller.

In order to see the signal, you can do it by the simulation tool such Modelsim.

By simulation your design in the tool, you can trace the waveform of your signal.

By right you can see the interaction of the mem_reset_n signal.

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi sir,

I hope you're doing great.

Do you still have further question on this case?

Regards,

Adzim

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Setting the case to closure.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page