- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

IP: UniPHY with DDR2 controller

Quartus Prime Standard 18.0

Simulation: Nios 2 + Uniphy + Micron DDR2 (MT47H128M16)

Modelsim-intel is used.

Problem: it stops during ddr2 initialization phase. It seems Uniphy IP doesn't follow Micron DDR2 initialization spec. I don't there is 200us which was required by datasheet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiaoqiang Shen,

UniPHY simulation does not adhere to the initialization timing to speed up the simulation so it will fail when using the Micron memory model. I assume the simulation passes with the DDR2 example design with Intel generated memory model. As a workaround, you can comment out the initialization time check in the Micron memory model.

Hope this helps.

Thanks,

Rashmi

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiaoqiang Shen,

Thank you for submitting the case. Will it be possible for you to share your design files to reproduce the issue at my end and further investigate.

Regards,

Rashmi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Xiaoqiang Shen,

UniPHY simulation does not adhere to the initialization timing to speed up the simulation so it will fail when using the Micron memory model. I assume the simulation passes with the DDR2 example design with Intel generated memory model. As a workaround, you can comment out the initialization time check in the Micron memory model.

Hope this helps.

Thanks,

Rashmi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

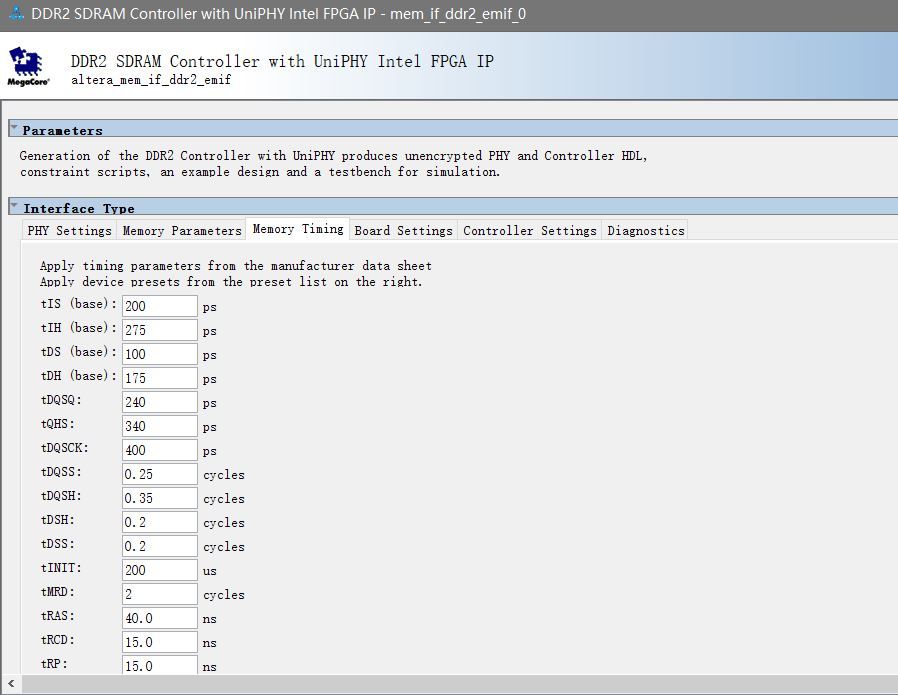

1) Actually it’s defined the tINIT = 200us when launch this UniPHY IP. The parameter is also compliant with Micron datasheet. Why UniPHY IP doesn’t consider it as it knows exact memory parameter.

2) If you look at my first question attachments, you will see UniPHY IP doesn't follow memory initialization sequence. For example: cke should stay 200us when power up.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Unfortunately, UniPHY simulation does not adhere to the initialization timing to speed up the simulation so it will fail when using the Micron memory model.

Which simulation option they have selected. You probably have "skip calibration" selected which is the default.Please change the setting to "full calibration" to get past the error but it will take forever (~4 days) to complete.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I used +define+ALTERA_ALT_MEM_IF_PHY_FAST_SIM_MODEL=0 in related files nios_mem_if_ddr2_emif_0_p0.sv and nios_mem_if_ddr2_emif_0_pll0.sv.

And modelsim shows message: # Using Regular core emif simulation models.

But it still doesn't work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does this latest sim run much longer than the previous simulation? It should be running full calibration

Can you please check how long mem_reset is asserted? It should stay low for at least 200usec in full calibration mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does this latest sim run much longer than the previous simulation? It should if you are running full calibration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Does this latest sim run much longer than the previous simulation? It should be running full calibration

Can you please check how long mem_reset is asserted? It should stay low for at least 200usec in full calibration mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page