- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We are using standard FPGA FFT IP for our design given by intel.

we want to use many FFT IPs parallely for that the problem that we are seeing is resources for ALMs required is not suffiecient with the fpga availability.

It has sufficient amount of dsp available in the fpga.

So, is there any way for that fft ip to consume some of the DSPs in the fpga for some part of logic instead of ALMs so that we can fit more parallel ffts in our design and use all the ALMs and DSPs effectively.

As this is critical for us any answer soon helps us a lot.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

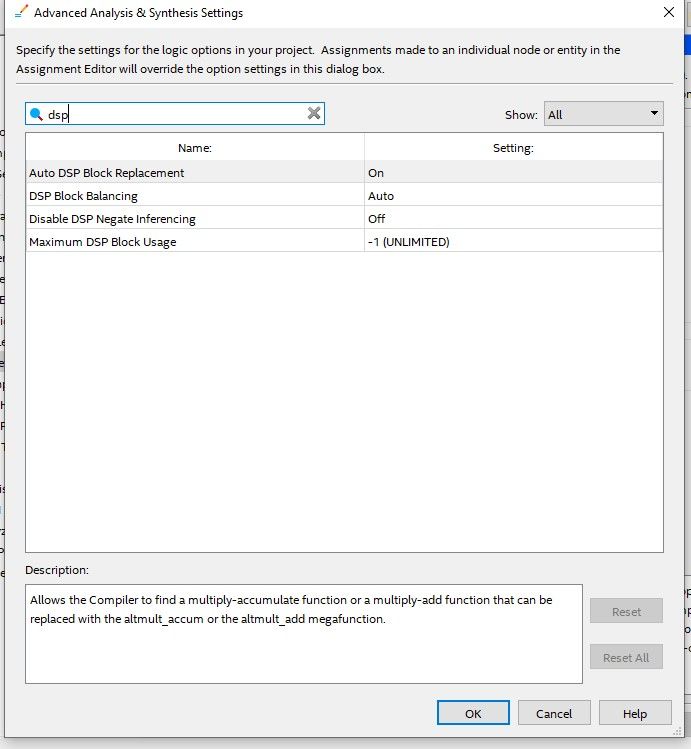

Those are the current settings right now we are using, is that correct?

will that setting make some of the DSPs freely available in fpga to be used as logic elements for FFT IP?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

That is the only setting you have. How much percent you have used for your DSP block? Did you get fitter error?

you can try to turn off the auto DSP block replacement if you want your DSP to be place in LAB but not in the DSP block. One Lab consist of 2 ALM, if your dsp logic does not put in the DSP block, it will put in the LAB.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

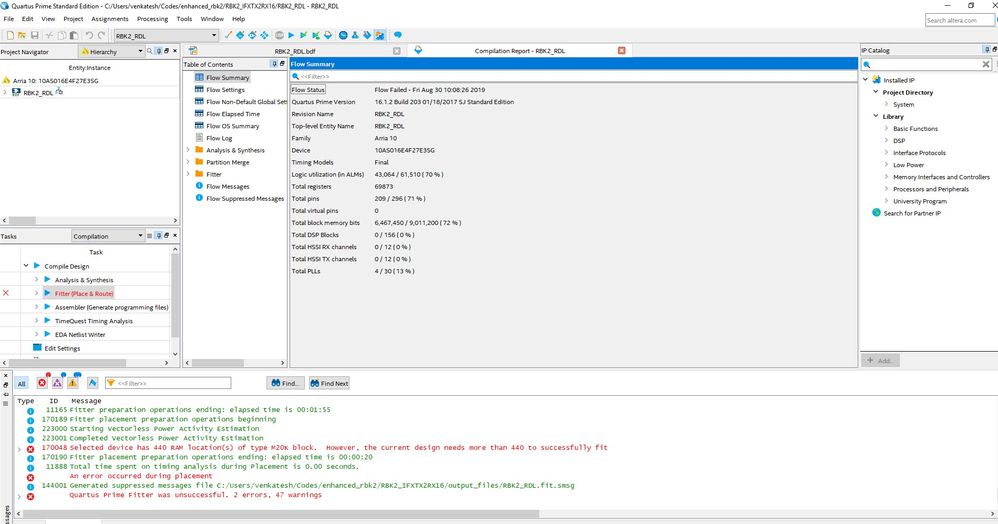

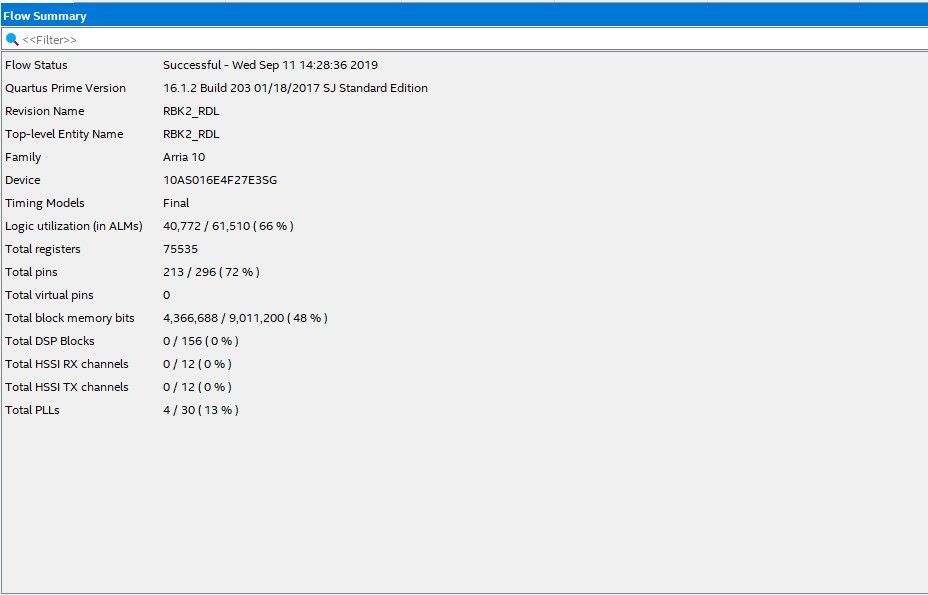

Resources usage summary report also added you can see.

--------------------------------

Now I am getting a different problem.

- None of the dsps getting consumed for fft ip in the design and all ALMS only consuming

- Even though 72% of M20K used , it is saying that fitter can't run as it requires more than 440 M20K.

I am using quartus 16.1.2

Why like this what's wrong in settings?

anything more to set and correct..?😏 😬

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) when you turn off the auto DSP block replacement, means it will switch to ALM

2) How many FFT IP that you have use in your design? Is that fine for your to have certain IP to use ALM totally?

3) unless the FFT IP have a setting for you to control the usage, but seems there dont have.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

1) when you turn off the auto DSP block replacement, means it will switch to ALM

-- I tried all the settings, none of the setting in it made it to take DSP consumed.

2) How many FFT IP that you have use in your design? Is that fine for your to have certain IP to use ALM totally?

-- Right now around 8 FFT IPs used of 2048 length each, but I need to use 8 more 256 FFT IPs too. I need ALMs to be free and let DSPs be used for the atleast allocated calculations according to datasheet. That is not happening now. According to datasheet it should consume some DSPs also so that the ALMs consumed will reduce.

3) unless the FFT IP have a setting for you to control the usage, but seems there dont have.

-- Unfortunately yes, I tried to see option in FFT IP given by INTEL, there is no option for DSPs selection related.

What kind of solution you guys propose now to make DSPs to be consumed for the respective logic atleast?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I would suggest to use Attribute on the rtl code. however, whether Quartus have this attribute to turn off dsp block have to find out.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

what kind of attribute..? Can you suggest me the exact answer what to do. because What can I do in rtl code now because everything is IP based and I am using bdf , no vhdl coding.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

you can try look for https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/qts/qts_qii51008.pdf if there dsp attribute.

also, if you look for 16-32, there are dsp balacing to help you auto convert the dsp to logic

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I looked in the PDF 16-32, that is telling about the option of DSP balancing when ALMs are not available how to use DSP blocks as slices, but my case is different right now for me whatever ALMs and DSPs block conusmption mentioned in FFT User guide are not matching with the current consumption.

As in the datasheet/user guide it is mentioned that DSP blocks will be consumed but in the actual scenario ALMs are getting consumed where I require ALMs for my other logic blocks to develop. So, I want the FFT IPs I added in my project I want DSP blocks for computation/multiplication logic to be consumed instead of ALMs.

My question is why that is not happening for the above synthesis settings i gave previously. To make it happen what to do?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It depends on the requirement of the frequencies that you set to the dsp. If quartus found that using the ALM can suite the frequencies that you use either than use the DSP block, Quartus are free to choose between DSP and ALM in your case.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Let us know if you still have any question on this? If it still unable to solve, we can chat offline.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Still As I told ALMs only getting consumed instead of DSPs . I just want to know that procedure only to force tool to consume DSPs for the respective logics atleast instead of ALMs. I don't see my clock in which I am going to operate is that much a big problem because I am using only 100MHz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

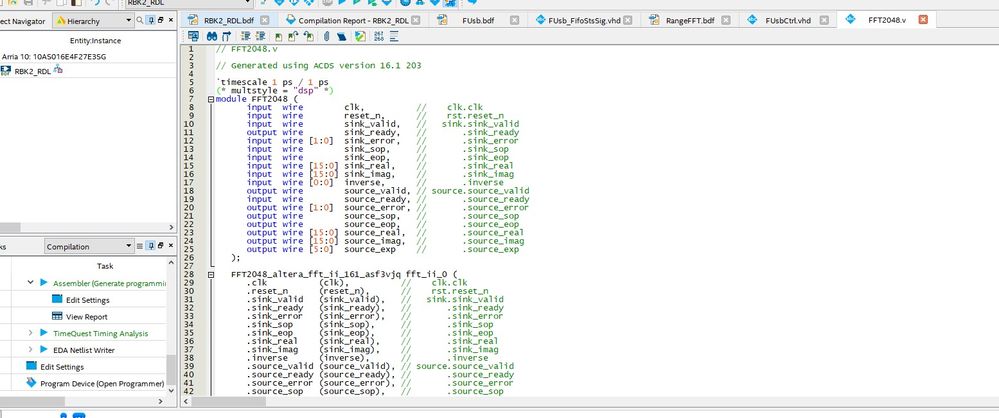

Remember the attribute that I suggest earlier? Here is the format of it:

It is called the Verilog multstyle attribute to inform Quartus that you want to use logic based multipliers. To do this, add the following line directly above the module definition:

(* multstyle = "logic" *)

For example, you might have:

(* multstyle = "logic" *) module someMultipler ( ...

This will tell Quartus to use logic for any multiplier in this module.

You can do the same to request DSP blocks as well, using

(* multstyle = "dsp" *)

With this you can selectively choose which module to use logic and choose which you want to use dsp.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yeah. Understood. but since it is a standard fft ip and i added that in a bdf. in which verilog file i should add this attribute?

i see in online you can apply this attribute to the verilog code. but you know when we deal with schematic view and bdf and standard ips where is the scope for verilog file to add this ?

still i tried to add this at the verilog file top module file generated by qsys of the ip. No DSPs are consumed after this trying also. refered the attribute syntax from the following link https://www.intel.com/content/www/us/en/programmable/quartushelp/17.0/hdl/vhdl/vhdl_file_dir_multstyle.htm

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What you can do is create a wrapper to wrap around this FFT2048 and with the top level name FFT2048_no_DSP and another name with FFT2048_with_DSP. After creating this two wrapper, you can create bdf out of it and use it to your bdf.

Since I had very long did not touch on bdf, i remember seeing customer use attribute in the bdf itself. But I can't remember how they have do it.

We dont really encourage user to use BDF anymore, we encourage user to use verilog and vhdl code. As it is really not that hard to used.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

what ever i have messaged about the usage is like using that attribute in a wrapper kind of code only. But still you can see 0% dsps used.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

May be you can create one simplified design and post it here. I will help you to sort this out.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

added a project with only fft2048 ip and added the attributes also. since I am used to vhdl , you will see top module with vhdl. here also same situation as discussed only ALMS consuming. quartus 16.1.2 I used. And for my other developments also using same quartus version.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for attaching the design.qar files. Looking into the FFT module, most of the .v is encrypted. DSP block usually was used when there are multiplication take place. Since those files are encrypted, you cannot force those design to use the dsp block.

Unless you create your own design, then you will have better control of it.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page