- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hello expert,

On our own Arrria10 board, we use "PCIE gen3x8 with AVMM-DMA (64bit)" setting.

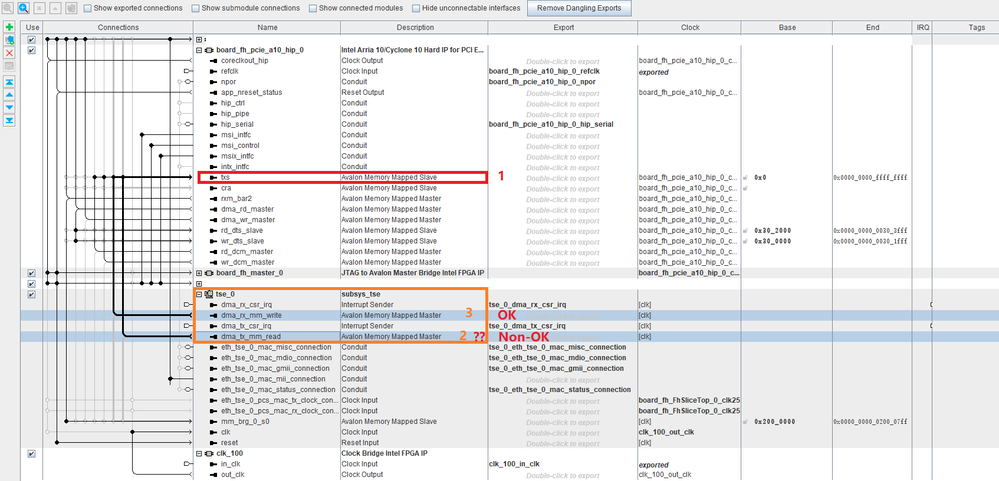

Per our system specific scenario, we have to add "MSGDMA + TSE " for ethernet i/f. But we met a "Txs_waitRequest_o deassert has too big delay " problem , detail as following :

[1] let's talk that marked number (3) in above picture, [Hip_Txs] connects to [TSE_subsystem -> dma_rx_mm_write] , which is the ethernet packet receiving path.

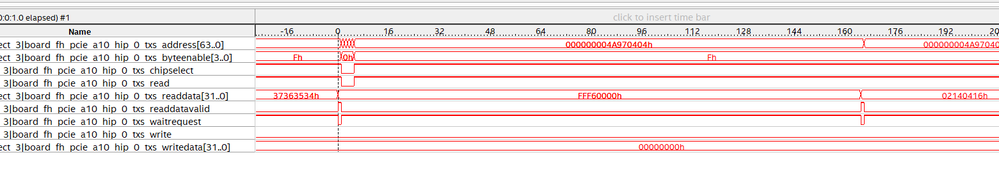

Firstly this recv path work fine as expect. From SigTap picture(below), we see per around ~10 clock cycles, "Txs_waitrequest" signal was deasserted to activate the mSGDMA write data through "Hip_Txs" into Host memory space. thus ethernet were transfered from fpga tse sub-system into Host memory correctly, and the transferring performance is correct.

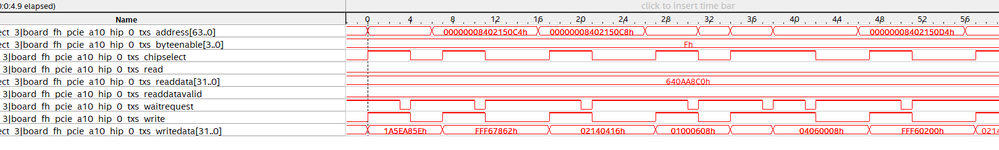

[Question] : why this big delay (~168 cycles) of "Txs_waitrequest" happens in mSGDMA reading direction? while the reverse writing direction the "Txs_waitrequest" behaviour good ?

[BTW], we uses "AVMM-DMA" setting in our system. We made an experiment to change from "AVMM-DMA" to "AVMM w/o DMA" in PCIe HIP core, in this case both "mSGDMA writing" and mSGDMA reading works fine, that says the “~168 cycles delay" disappears, this maybe some clues for your expertised analysis.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

hi SK, you'r expert of A10 PCIe HIP Core, would you please help on this issue ?

If need more debugging trace, we can provide.

thanks very much~

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Intel, we didn't receive any reply about the problem we reported, could any expert give an advice how to move forward? we 're stuck really since our performance test failed now. Thanks in advance ~

cc @KhaiChein_Y_Intel ,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

kindly reply

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page