- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

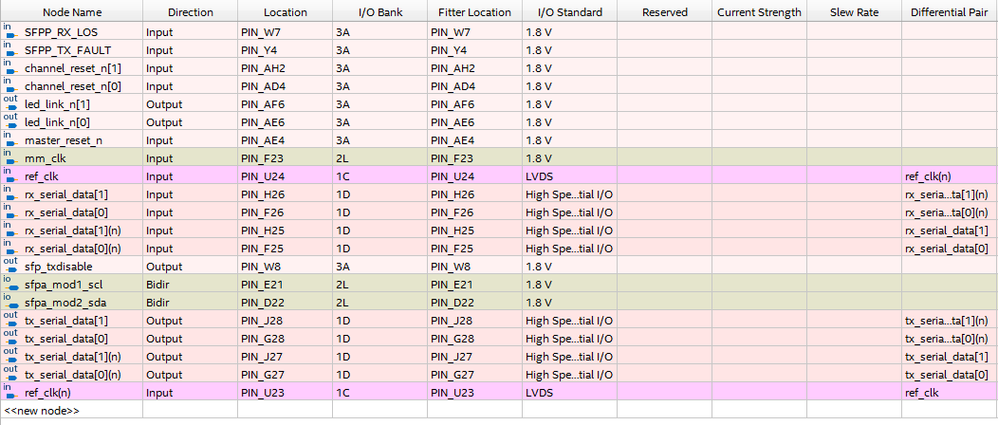

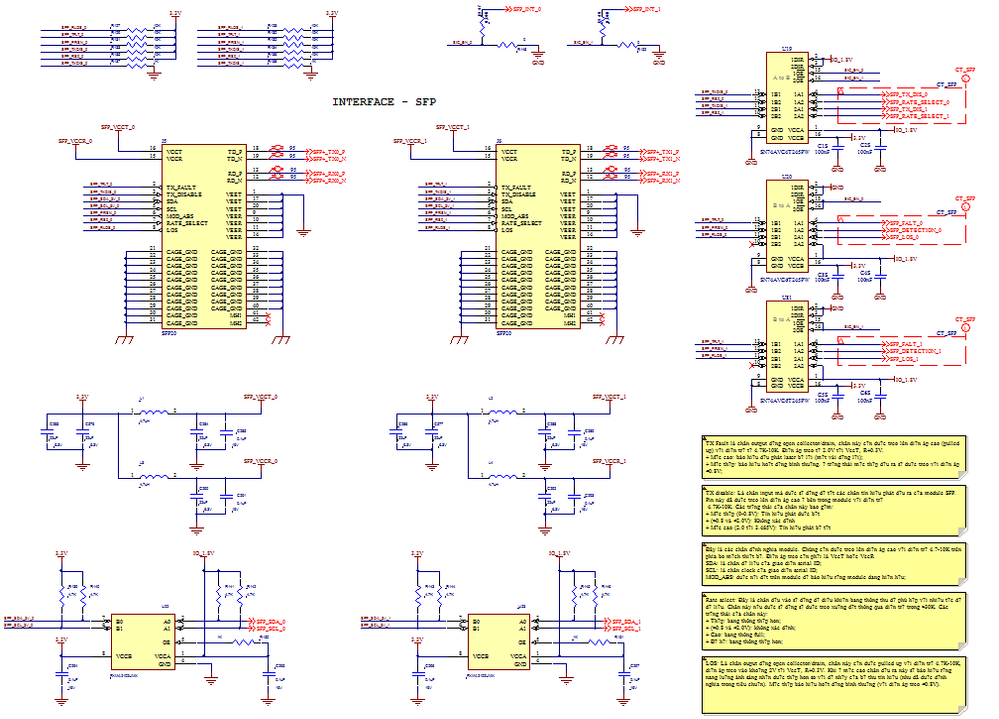

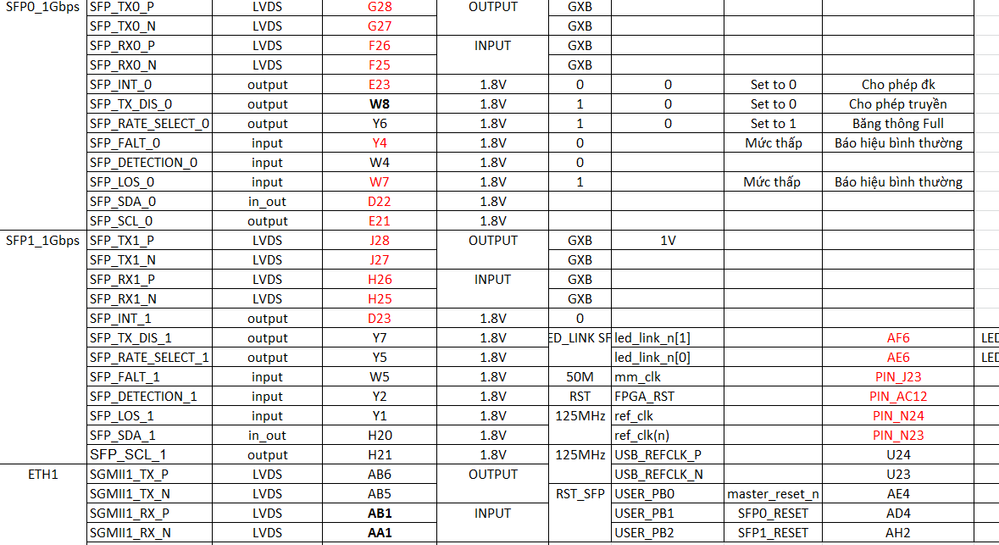

I am designed a custom Broad with Cyclone 10GX and 1G SFP interface. I am using project test altera_eth_tse_native_phy_w_1588. I have been run TEST_PHYSERIAL_LOOPBACK and TEST_SMA_LB was succesfull in my Custom broad and Cyclone10GX deverlopment kit. But, when I was running TEST_1588 0 1 1G. Project could not transmitted frame succesfull. Can you show me where the error is or give me a project test with sfp use TSE ipcore

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SengKok! All issues have been resolved. This error is caused by CLK signal for GXB. My custom broad Cyclone10GX ran successful 2 port SFP 1000 Base-X and 2 port 1000 Base-T. Thank!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is the problem only happen in your custom board, where there C10 GX development board is working fine?

Do both channels pass the TEST_SMA_LB test?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have tested successfully with TEST_PHYSERIAL_LOOPBACK and TEST_SMA_LB in both broad (My custom broad and C10 GX development board). Moreover, I do not understand why when I disconnect SFP cable TEST_SMA_LB still successful. This is my project test in Quartus 18.0 https://drive.google.com/file/d/1F2bbFeMCh-TXbeFQpxwCKBGHeSaQj4gC/view?usp=sharing

Can you give true project test SFP 1G for Cyclone10GX. I need ping from my computer to custom broad over SFP module and TSE IP.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SengKok! My team has build a project ping test success from Computer/Bercut <-> RJ45 caple <-> 88E1111<-> SGMIII<-> TSE IP. Can you help me change to project test to Computer/Bercut <-> SFP Caple <-> SFP 1G module<-> XCVR<-> TSE IP? Thank so much! My project test is below. https://drive.google.com/file/d/1aZt2EIvVLVoqDmtknu724jLimWsUk57V/view?usp=sharing

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The following TSE design example may be helpful for your design migration:

Regards -SK

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SengKok. I have been tried "AN744: Scalable Triple Speed Ethernet Reference Designs for Arria 10 Devices" but projet not ran in TEST_1588 0 1 1G test in above. In project "Single-Port Triple-Speed Ethernet and On-Board PHY Chip Reference Design - Arria 10 " TSE run in SGMII interface with 88e1111. But I need interface with SFP port.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If the SMA loopback on channel 0 is passing, then please focus on your hardware setup first.

TEST_SMA_LOOPBACK 0 1G 1000

Please check if the channel 0 SFP loopback is passing.

TEST_1588 0 0 1G

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I can't sucess this test. I'm not sure that the Cyclone 10gx supports 1G SFP communication or I have misconfigured IPCore TSE. Can you help me try the above example on a Cyclone10gx kit. If that fails I fear that having to switch to using Xilinx IC:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You can follow the AN744 TSE IP core configuration for the settings. What you need to do is basically enable the GXB interface and then hook up with a reset controller. Please refer to the altera_eth_channel.v file.

Does the PHY internal serial loopback test is passed (TEST_PHYSERIAL_LOOPBACK 0 1G 1000), if yes, which means the TSE IP configuration and connection are fine.

Next, please confirm if SMA loopback or SFP loopback is passing on the same channel. If not, please capture the following signals for debugging:

- led_an

- led_link

- pll_locked

- tse_reset

- rx_ready

- tx_ready

- rx_is_lockedtodata

- rx_is_lockedtoref

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi. SengKok_L_Intel. I have been test successful Ping from Bercut to Cyclone 10GX kit use TSE ipcore over SFP 1G module. But when I test in my custom broad have error (Can't setup Ethernet link synchronization). My broad similar DEV 10GX kit. All signal ok such as ref_clk = 125m; SFP_TX_DIS_0 =0; SFP_FALT_0 = 0 but no signal in SFP_RX0_P and SFP_RX0_N. So I think XCVR_Native in my Broad error. I try test XCVR using "Cyclone 10 GX XCVR Toolkit Reference Design v17.1.1 User Guide" on tranceiver toolkit has eror below.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

XCVR and TSE ping tests ran in Cyclone 10GX KIT but not ran in my custom board. Can you tell me why and how to fix the above problem to work properly XCVR? VCCT_GXB = VCCR_GXB = 1.03V; VCCH_GXB = 1.8V and all signal TX and RX same in both my wide KIT and custom DEV.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

What is the difference between the dev kit and your custom board? Is your custom board passed the internal loopback test?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi SengKok! All issues have been resolved. This error is caused by CLK signal for GXB. My custom broad Cyclone10GX ran successful 2 port SFP 1000 Base-X and 2 port 1000 Base-T. Thank!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

If further support is needed in this thread, please post a response within 15 days. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page