- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

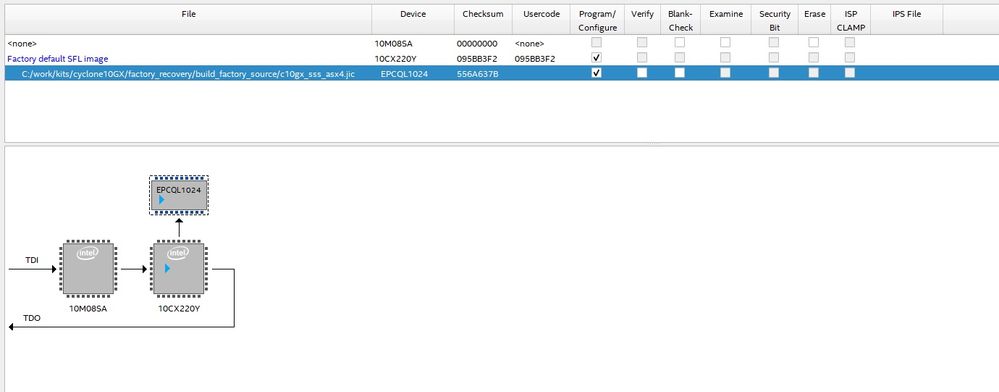

Using the C10 CVP sample project I added the Serial Flash Loader IP to the design into the top_hw.v.

I setup the jtag chain for the Cyclon 10 GX Dev. Kit, download the 10 design (sof) -> ok and download of the jic file starts -> error Flash Loader IP not loaded on device 3. AS is enabled (S1.x default). Unlike with other designs detecting of the jtag chain does not show the epcql1024. The cyclon 10 design is loaded with the right jtag usercode, as a try.

Ссылка скопирована

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

I think your own design does not have the SFL design which is needed to program the flash. When you attach the jic file to the Cyclone 10 GX, you shouldn't modify the file but use the factory default program to program into the FPGA so that the SFL is loaded.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi John

Thank you for your prompt answer. I tried to download as proposed and I am afraid it did not work. See screenshot below. A very worring thing is the readme file in the factory_recovery folder, containing the following sentence: "Note: .jic file cannot be programmed via Quartus Prime Programmer at this moment, will be fixed later in v18.0 or later build." Is this working indeed now?

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

I observed that you are still not programming the SFL image into the Cyclone 10 GX device. Below is the screenshot that you should observed.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hello John

I seem to miss something. Obviously I took the c10gx_sss.sof file found in the build_factory_source folder. What you are telling me is this is not the right image to take? How to choose the "right" design to do so?

Thank you!

Roland

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hello John

Thanks a lot, I appreciate your help! Due to Corvi 19 restrictions I can not try today.

Best regards

Roland

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hii, may i how you created .hex file for that .jic file. And for EPCQL1024 flash how you assigned memory for .sof and .hex while creating the .jic file

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Sure. Will wait for you update again once you are able to test it.

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hello John

I was able to download the jic to the device. Thank you for this.

Correct me if I am wrong: if I includ the flash loader ip into my design, after power up the programmer should recognize the epcql1024 when scanning the chain?

Thank you!

Roland

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

Hi,

Yes, if you have Serial Flash Loader IP in your design then the programmer should be able to recognize it after power up.

- Подписка на RSS-канал

- Отметить тему как новую

- Отметить тему как прочитанную

- Выполнить отслеживание данной Тема для текущего пользователя

- Закладка

- Подписаться

- Страница в формате печати

![2020-03-16 14_51_24-Quartus Prime Programmer Pro Edition - [kit.cdf]_.png 2020-03-16 14_51_24-Quartus Prime Programmer Pro Edition - [kit.cdf]_.png](/t5/image/serverpage/image-id/1695iD17AC634A8417ADA/image-size/large?v=v2&px=999&whitelist-exif-data=Orientation%2CResolution%2COriginalDefaultFinalSize%2CCopyright)

![2020-03-17 08_28_44-Quartus Prime Programmer Pro Edition - [devkit.cdf]_.png 2020-03-17 08_28_44-Quartus Prime Programmer Pro Edition - [devkit.cdf]_.png](/t5/image/serverpage/image-id/1702i0AEF6B40D091B15D/image-size/large?v=v2&px=999&whitelist-exif-data=Orientation%2CResolution%2COriginalDefaultFinalSize%2CCopyright)