链接已复制

Hi,

First of all, I want to make it clear, use for FPGA board is Ok, but for simulation, HPS used Mentor VIP.

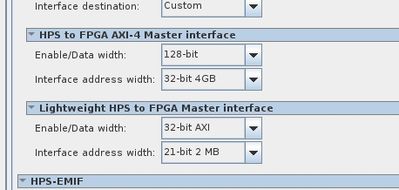

Are you see in synth or sim directory? At the same time, "HPS to FPGA AXI-4 Master interface" Enable/Data width : 256-bit, then you can compare the file for synth and sim directory, the synth directory is S2F_DATA_WIDTH mismatch with sim directory. "HPS to FPGA AXI-4 Master interface" Enable/Data width : 128-bit, The compare data width is Match.

Then I found other question, as following.

AXI4 Don't support AXI_USE_WUSER.

Hi,

I have tested multiple tests, using the GHRD on Quartus 22.2, after Upgrading the IP, I am able to see the changes correctly for both synth and sim, and for all settings.

Could you try using the GHRD?:

Hi,

Thanks for the info, I have seen the case and the fix will be in Quartus 23.2, we apologies for any inconvenience in our support we appreciate your feedback.

If no further related questions, could we close the thread?

Hi,

I hope that your question has been addressed, I now transition this thread to community support. If you have a new question, Please login to ‘https://supporttickets.intel.com’, view details of the desire request, and post a feed/response within the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you on your follow-up questions.

p/s: If any answer from the community or Intel Support are helpful, please feel free to give best answer or rate 4/5 survey.