- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, I am using the de10-nano dev board and I have modify the DE10_NANO_SoC_FB demonstrations, which is used for LXDE desktop

I want to know how to access the ram address on linux system with FPGA.

I've declare a huge array with c and send the address to FPGA through PIO, but i cannot read or write the address,

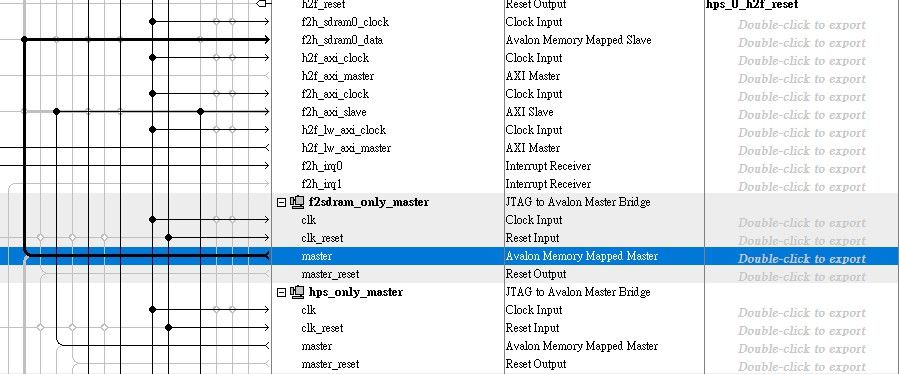

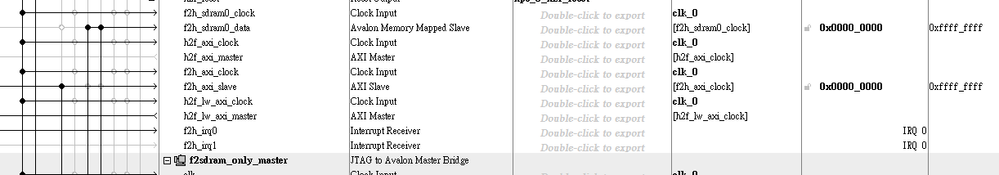

the default qsys connect f2g_sdram0_data to f2sdram_only_master

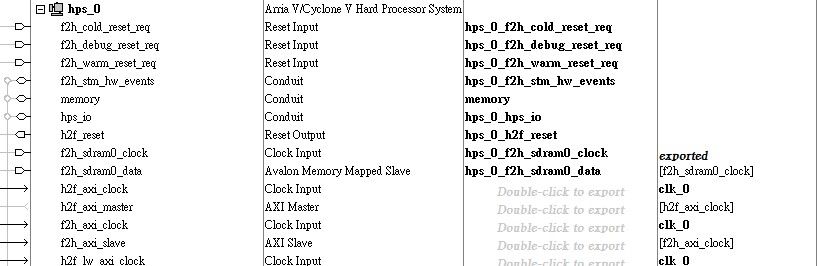

if i export the f2g_sdram0_data pin the OS won't start.

How could I access ram address like &arr directly on FPGA

furthermore, when I want to access the sdram through f2h, I add additional sdram interface, but the wait ready signal has never been set

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I would like to know what do you want to do with your design?

Is it sending data from FPGA to HPS? or reading HPS SDRAM via FPGA?

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We want to storage an huge array (around 20Mbit) by HPS into SDRAM and read it with FPGA once HPS finish the assignment.

durning the FPGA operation there's around 10M bit data we have to temporally storage, and we want to storage it in SDRAM.

the c program will never operate the these memory when FPGA is operating

we are using the PIO to use specify address to serial input each data, now but we think the program could be accelerated when FPGA can read SDRAM directly.

Thank you for replying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

You can access the SDRAM from FPGA directly through the f2sdram bridge. It should be much faster than the PIO.

You can refer to the DE10-Nano examples from Terasic. They provide an example of how to transfer data from FPGA to HPS and vise versa.

Please let me know if you need further help.

Thank you

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, FJumaah.

we are student of the same lab.

We have modify the DE10_NANO_SoC_FB demonstration. I know the DDR3-RTL demonstration has the f2h-sdram access method,

but we want to access the f2h_sdram from FPGA directly with the LXDE desktop, so we use the DE10_NANO_SoC_FB demonstration to do,

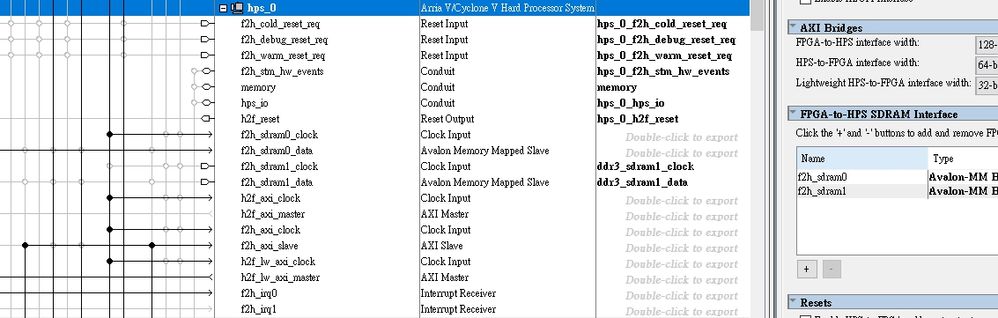

And the f2h_sdram parameter is different between the DE10_NANO_SoC_FB and DDR3-RTL, so i don't know how to use ...

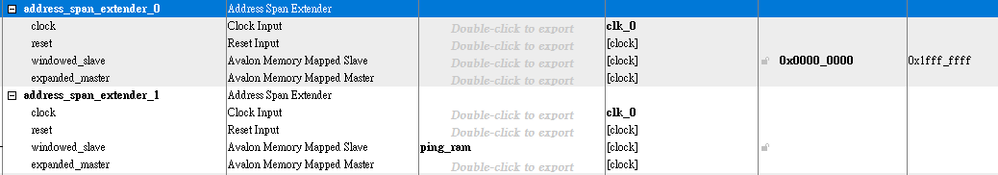

The Linux system use the top 512MB address (0x0 - 0x1fffffff) , and i want to use (0x20000000 - 0xffffffff) address locate through the f2h_sdram from FPGA.

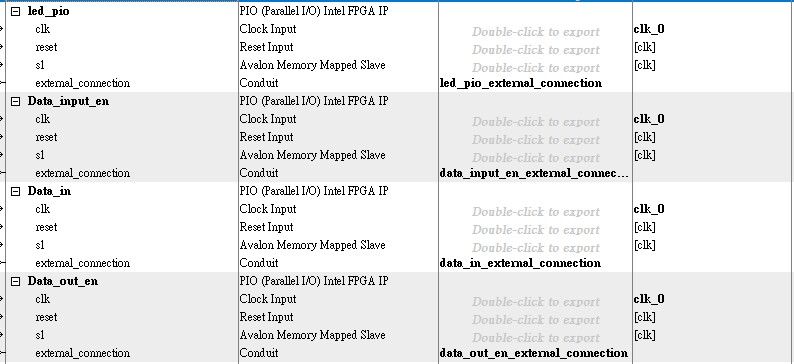

This is our system contents of the Qsys.

We try to use two address_span_extender to control the sdram address range.

One is used limit the Linux system usage (0x0000_0000 - 0x1fff_ffff),

The linux system is working on the FPGA.

Another if use to access the (0x20000000 - 0xffff_ffff ) address

but when i access the second one, The linux system will crash, and the results is not correct.

We don't know how to access the f2h_sdram with the LXDE desktop ( DE10-NANO-SoC-FB)

Thank you for replying

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

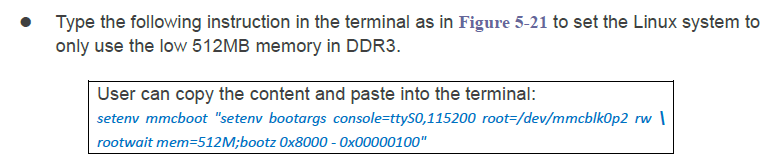

Do we need to set the LXDE sdram usage like the DE10-Nano User Manual page.76?

But this is for linux system, not the LXDE desktop. How can i do, or have any document i can find the command line.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

This can be done for both LXDE and command line versions.

This command is useful to let the kernel assign the lower portion of SDRAM to kernel space. The rest (except the hard registers) will be assigned for user space.

thank you

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page