- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We are building using the Quartus 11.1sp1 version (yes that is old but we have no reason to upgrade at this time)

I found where I can remove “DEAD” codespace by adding this to my Compiler options:

-fdata-sections -ffunction-sections

And also adding this to my LINK options:

--gc-section

For our Fast Fare this worked and my codespace is now smaller, but for our Fast Fare-e (which uses more RAM) I get the following ERROR.

On the “nios2-elf-g++” command to do the LINK:

OutOfMemoryError: Java heap space

make[3]: *** [farebox__fastfare-e__release.elf] Error 1

make[3]: *** Deleting file `farebox__fastfare-e__release.elf'

make[3]: Leaving directory `C:/altera/fastfare/software/app/farebox'

make[2]: *** [.gfi_elf] Error 2

make[2]: Leaving directory `C:/altera/fastfare/software/app/farebox'

make[1]: *** [.gfi_build] Error 2

make[1]: Leaving directory `C:/altera/fastfare/software/app/farebox'

make: *** [fastfare-e.release.gfi_build] Error 2

There is virtually no difference in these two builds and the code is 85% the same but there are bigger RAM buffers in Fast Fare-e due to a larger Display (so bigger Virtual GUI Buffers).

How do I fix this so I can remove DEAD CODE from the build??

For now I removed the options and I am building fine...

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May i know the BSP setting?

By clicking as below:

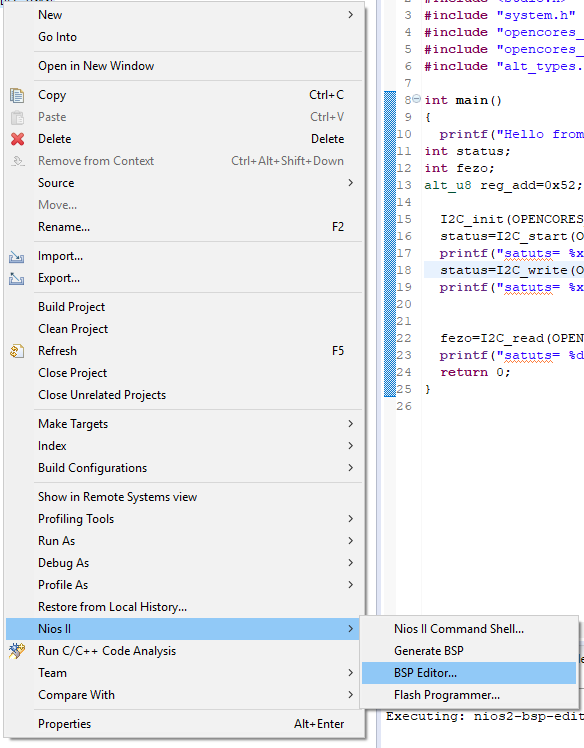

-right click the bsp project

-click Nios

-click BSP editor

The steps mentioned as below:

May you try to screenshot the main screen and linker script screen of the window open?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

There is no attached file found here.

May you try to attached again?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It has been a few days, did you get the attachment and you are looking at it???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Yes, I am looking into it.

There are two workarounds that you may try:

- Change some BSP settings via the BSP editor. ie reduced driver, optimization, small c library, clean exit.

- Increase on-chip memory size

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Increasing RAM Size on the boards is out-of-spec, we have 15,000 boards already in-service that new S/W updates.

As I stated, it has be "a while" since I tweaked any settings in the BSP.

Please list EXACTLY what you want me to change in the BSP (not loose terms) including FROM and TO values and I can try that!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Have you decided what EXACTLY (including WAS/NOW) in the BSP you want me to change?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It is not guaranteed that if you choose the small C library, the design will fit inside your memory. You can give it a try and then if it gives you the same error you must increase the On-Chip memory or use an external memory if your code is huge. I recommend you to start first increasing the memory size. BTW what is the memory size you are using right now?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The EPCS is 8M and we have no problem fitting in that (code only no RAM) even though GCC Build thinks it won't fit due to us putting a BOOT (small code and FPGA load) in 1MB of EPCS and a ZIPPED Application in remaining 7MB. GCC Build thinks APP won't fit (and without being ZIPPED it probably wouldn't).

RAM is 16MB Total which must fit the APP code (no FPGA since that is loaded by BOOT) and all RAM variables.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am confused, which memory you use to keep the code and which for execution?

Can you tell us what are the NIOS II vectors? reset vector and Exception vector.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have an 8MB EPCS Flash and 16MB RAM and he RESET vector points to EPCS (BOOT).

- Lower 1MB of this is FPGA and BOOT

- Upper 7MB of this is our (zipped) APP ... which is built with SAME FPGA as BOOT (but does not have another copy)

At Power Up:

- The FPGA is loaded by H/W from EPCS Flash

- The BOOT is copied into RAM and Vectored to in RAM by H/W

- BOOT sees APP image in EPCS is VALID and unzips it to RAM and jumps to it (BOOT is now DONE)

- APP image runs out of 16MB RAM (using FPGA loaded from BOOT)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

So if you are booting from the EPCS you can use the following:

1- Use "small Hello wold template" which turns off all the unnecessary libraries

2- Use optimization -O2 in the project settings.

These two options will give you the smallest code size of your application. If you still facing the same error you can use the XIP "Execute In Place" to save more size of the RAM which won't copy the .text region of the code to RAM (If the EPCS can fit the design)

In case if the EPCS cannot fit the design (FPGA+Zipped app) you can try:

- To configure the FPGA from another memory.

- Upgrade the EPCS flash. Configure the FPGA and Boot NIOS from EPCS with XIP on RAM.

- Upgrade the RAM and Configure the FPGA from EPCS and Run the NIOS on RAM.

Otherwise I apologize if the design still out of memory, I have no clue to shrink it more than this to fit into the RAM and EPCS. Please let me know how can I help you.

Regards,

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page