- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

(1) We have compiled and loaded the pam4_xcvr_com design example that came with the Board Test System (using Quartus 18.1.2.277) into our Production Stratix 10 SI system. The SI Quickstart Guide says to hook the board SMA outputs to an oscilloscope, but it doesn't say what kind of scope, or how to trigger it. We haven't been able to display the PAM-4 eye on our DCA using any of the output clocks. How do we trigger it? Is an external clock source needed? (We've tried that too, without success so far.) We see something that looks like a 4-level signal when we capture samples on a real-time scope. But we cannot produce an eye.

(2) when all PAM4 channels are turned off (using the "Transceiver toolkit") we still see a signal on the SMA outputs. It looks like a ~7GHz distorted sine wave. We can trigger this one with the PLL output clock signal (at ~156 MHz). What signal is this?

(3) in order to get Programmer to load the design, I removed the Max V from the JTAG chain (setting SW1-2 to CLOSE/ON). Is that the correct way to load and run the design?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hie,

Please check my replies to your questions above:

- To be able to observe PAM4 signals you will need to use a Real Time Scope (RTS) or Sampling Oscilloscope that support PAM4. The Rx architecture is different between NRZ and PAM4, hence you should be using a DCA that supports PAM4. As for whether external clock is required; RTS don't require external clock but some sampling scopes require it. However, the newer sampling scopes has a build in clock recovery module that don't require external clock trigger (typically sourced from the reference clock to Tx PLL or recovered clock from CDR). Please refer to your scope's applications notes on measuring PAM4 signals to understand if external clock source is needed. Also, due to non-linearity of the PAM4 eye's, you will need some level of soft equalization or FEC (typically soft feature in the scope) to be enabled to observe a clean eye. Please check this in the scope application notes on what to enable to observe the eye.

Regards,

Nathan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Replies to remaining questions:

2. Could you attach the scope snapshot so I could understand further whether its showing the signal tri-stated or not. If you turn off the channels using toolkit, the channels are not powered down but tri-stated.

3. Yes. this is the method to choose which device (MAX V or Stratix 10 ) to program. Yes, after selecting the correct SW setting, then you can program the device using Quartus Programmer.

Regards,

Nathan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

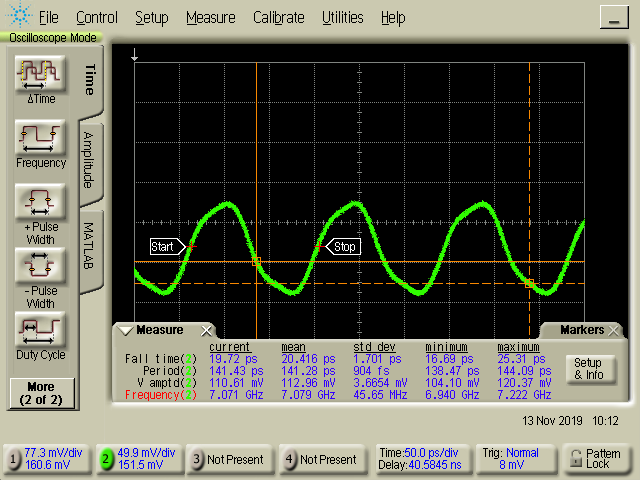

Here is the requested scope trace. I hope you can read it. We get this signal from the SMA outputs when the transceiver TX is off. Its frequency is ~7.0GHz. I triggered this signal it with itself, using an 8x frequency divider to get the trigger frequency in range. If I use one of the PLL output clocks (156.25 MHz) as a trigger instead, I get a composite of copies of this signal with three different starting phases.

We still haven't managed to trigger the 51Gbps PAM-4 output. Any suggestions or instructions would be greatly appreciated. (Please see my previous comment about our DCAs.) Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello Nathan,

Thank you for your reply. We are able to create 25GBaud PAM-4 signals with a high-speed DAC and display eyes on our DCA without problems. (I have access to two DCAs that can do this and have tried both.) Our DCAs are not bleeding edge technology but still seem sufficient. The main constraints are (1) that the trigger cannot be too fast (I believe 2 GHz is the limit, I don't remember) and (2) the symbol rate should be an _exact_ multiple of the trigger signal rate. Because of this constraint, we've tried applying an external clock with a rate which divides the symbol rate to the various PLL clock inputs on the SI board, including the one for the specific e-tile that generates the SMA outputs (9A as I recall). We still can't get the signal to trigger. It's not just a matter of having a closed eye. We've tried external clocks in the 100-156.25 MHz range. I wonder if maybe our 500 mV input clock signal is too low? We are driving it single-sided, not differential. By the way, as you suggest, I can capture traces with a real-time scope, but this is not what we want. Thank you again for the help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I believe the limitation is on the scope trigger limitations.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Well, I used the "ClockController.exe" app and changed clock 0 from 156 to 176 MHz; that apparently solved the problem. I suggest including some triggering instructions in the next release of the "Quick Start Guide."

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hie,

It seems your issue was related to the frequency for the clock generated from the Stratix 10 TX development kit was not correct. I should have pointed you to the Development Kit's user guide.

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug-intel-s10-tx-devl-kit.pdf

The information on the ClockController is covered in section 5.3.11. Anyway will provide feedback to consider incorporating information about configuring the clock controller frequency in the Quick Guide.

Regards,

Nathan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, OK, thank you. That would be helpful to people, surely. I guess my thinking was that the BTS and the design examples would work "out of the box," so to speak. The Quick Start Guide certainly gives that impression. In any case, thank you for the help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, Thanks for your feedback as well.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page