Hi, I am writing to ask a question about the pull-up and pull-down resistors used in JTAG signals.

If an FPGA has internal pull-up resistors, do I need to add these resistors? If I do need to add these resistors, do they need to be placed close to the programming port, or is there no such requirement?

I would appreciate any information you can provide on this topic.

Thank you for your time and consideration.

Hi,

Yes, FvM is correct. Diodes and capacitor are more critical. The position of the resistor in your design should be fine.

Regards,

Aiman

链接已复制

Hi,

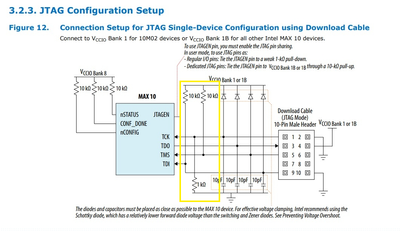

It is recommended to follow the setup in the userguide. For the resistor, it should be put close to FPGA.

Regards,

Aiman

Thank you for your reply.

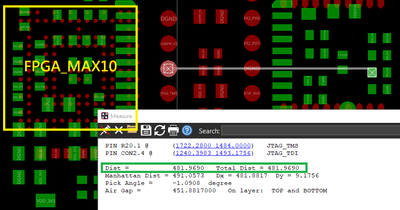

Since my PCB is very small, only 36mmX36mm, there are some difficulties in placing the components.

If the distance is as shown in the figure, will there be a problem? Or is there a maximum allowable length?

482mil (12mm)

Hi,

Yes, FvM is correct. Diodes and capacitor are more critical. The position of the resistor in your design should be fine.

Regards,

Aiman

We do not receive any response from you to the previous answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you