- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

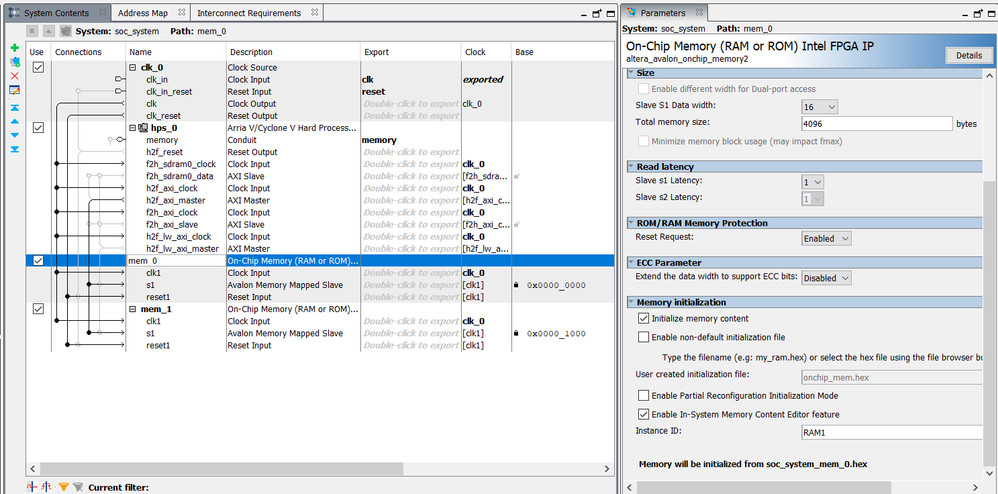

I'm using a Atlas-Soc (DE0-Nano-SoC) from the altera university program. It has a Cyclone V FPGA with a HPS in-built.

I usually connect to the Linux running on HPS through serial terminal (PuTTY). But in some cases as soon as i program the FPGA the terminal turns unresponsive. Any input I give doesn't reach the HPS.

This behavior can also be clearly seen on the Board. There are red and green lights to indicate RX and TX on the serial port on the board. Once the terminal turns unresponsive, any key stroke will flash the red led (TX led) but the Green Led doesn't flash indicating that there is no response from the HPS side.

Can anyone pls explain why this is happening? I'm also attaching the QSYS system and the FPGA code

//=======================================================

// This code is generated by Terasic System Builder

//=======================================================

module sdram_sdcard_write_test(

//////////// CLOCK //////////

input FPGA_CLK1_50,

input FPGA_CLK2_50,

input FPGA_CLK3_50,

//////////// HPS //////////

inout HPS_CONV_USB_N,

output [14:0] HPS_DDR3_ADDR,

output [2:0] HPS_DDR3_BA,

output HPS_DDR3_CAS_N,

output HPS_DDR3_CK_N,

output HPS_DDR3_CK_P,

output HPS_DDR3_CKE,

output HPS_DDR3_CS_N,

output [3:0] HPS_DDR3_DM,

inout [31:0] HPS_DDR3_DQ,

inout [3:0] HPS_DDR3_DQS_N,

inout [3:0] HPS_DDR3_DQS_P,

output HPS_DDR3_ODT,

output HPS_DDR3_RAS_N,

output HPS_DDR3_RESET_N,

input HPS_DDR3_RZQ,

output HPS_DDR3_WE_N,

output HPS_ENET_GTX_CLK,

inout HPS_ENET_INT_N,

output HPS_ENET_MDC,

inout HPS_ENET_MDIO,

input HPS_ENET_RX_CLK,

input [3:0] HPS_ENET_RX_DATA,

input HPS_ENET_RX_DV,

output [3:0] HPS_ENET_TX_DATA,

output HPS_ENET_TX_EN,

inout HPS_GSENSOR_INT,

inout HPS_I2C0_SCLK,

inout HPS_I2C0_SDAT,

inout HPS_I2C1_SCLK,

inout HPS_I2C1_SDAT,

inout HPS_KEY,

inout HPS_LED,

inout HPS_LTC_GPIO,

output HPS_SD_CLK,

inout HPS_SD_CMD,

inout [3:0] HPS_SD_DATA,

output HPS_SPIM_CLK,

input HPS_SPIM_MISO,

output HPS_SPIM_MOSI,

inout HPS_SPIM_SS,

input HPS_UART_RX,

output HPS_UART_TX,

input HPS_USB_CLKOUT,

inout [7:0] HPS_USB_DATA,

input HPS_USB_DIR,

input HPS_USB_NXT,

output HPS_USB_STP,

//////////// KEY //////////

input [1:0] KEY,

//////////// LED //////////

output [7:0] LED,

//////////// SW //////////

input [3:0] SW

);

//=======================================================

// REG/WIRE declarations

//=======================================================

wire hps_reset;

//=======================================================

// Structural coding

//=======================================================

soc_system integrated_system (

.clk_clk (FPGA_CLK1_50), // clk.clk

.reset_reset_n (hps_reset), // reset.reset_n

//HPS ddr3

.memory_mem_a ( HPS_DDR3_ADDR), // memory.mem_a

.memory_mem_ba ( HPS_DDR3_BA), // .mem_ba

.memory_mem_ck ( HPS_DDR3_CK_P), // .mem_ck

.memory_mem_ck_n ( HPS_DDR3_CK_N), // .mem_ck_n

.memory_mem_cke ( HPS_DDR3_CKE), // .mem_cke

.memory_mem_cs_n ( HPS_DDR3_CS_N), // .mem_cs_n

.memory_mem_ras_n ( HPS_DDR3_RAS_N), // .mem_ras_n

.memory_mem_cas_n ( HPS_DDR3_CAS_N), // .mem_cas_n

.memory_mem_we_n ( HPS_DDR3_WE_N), // .mem_we_n

.memory_mem_reset_n ( HPS_DDR3_RESET_N), // .mem_reset_n

.memory_mem_dq ( HPS_DDR3_DQ), // .mem_dq

.memory_mem_dqs ( HPS_DDR3_DQS_P), // .mem_dqs

.memory_mem_dqs_n ( HPS_DDR3_DQS_N), // .mem_dqs_n

.memory_mem_odt ( HPS_DDR3_ODT), // .mem_odt

.memory_mem_dm ( HPS_DDR3_DM), // .mem_dm

.memory_oct_rzqin ( HPS_DDR3_RZQ) // .oct_rzqin

);

endmodule

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So you're booting the HPS first to Linux before configuring the FPGA. What method are you using to program the FPGA at this point? Are you just using the Quartus Programmer or maybe a bare metal application to have the HPS program the FPGA?

#iwork4intel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Yes, I'm booting the HPS first to Linux before configuring the FPGA. The HPS boots as soon as i power the device, is there a way to stop this or postpone the boot process?

I'm using the JTAG Quartus programmer to program the FPGA.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you try enabling the bridges?

https://www.intel.com/content/www/us/en/programmable/support/support-resources/knowledge-base/embedded/2016/how-and-when-can-i-enable-the-fpga2sdram-bridge-on-cyclone-v-soc.html

I would also suggest you check this link, which have a lot of information on Programming FPGA, Booting Linux etc2:

https://rocketboards.org/foswiki/Main/GettingStarted

Select Cyclone V> your Quartus version> topic that you are interested in.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hey, @sstrell do you know how can i solve this issue?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page