- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi )

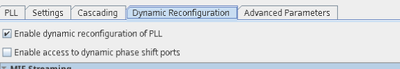

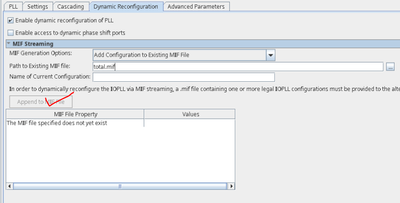

I want to generate PLL with mif setting for 5 clock speed.

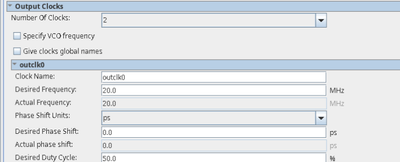

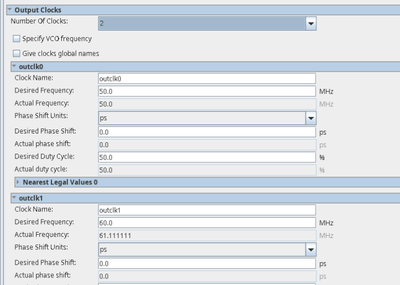

for example, input clock is 100MHz, I want to generate PLL which have 2 output clks.

but it should be reconfigurable with mif files.

Output clock used 30,40,50,60,60 Mhz

2)

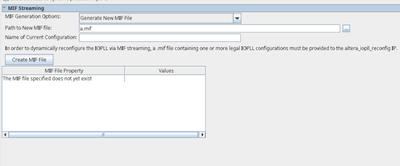

with 2 options, 1 mif file is generated for 30 Mhz and 40 Mhz.

with this , MIF can be updated.

This is OK , but for the RTL simulation how to change from 20 Mhz to 60Mhz ?

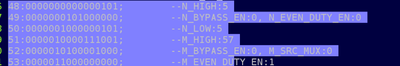

if 60Mhz option start 48 = 30 (hax)

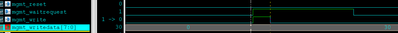

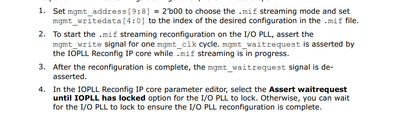

I put address = 0 ( mig option is [9:8] = 0 )

and mgmt_writedata = 30(hex )

mgmt_write

than waitrequest is 0 --> 1 and again 1-->0

but output clock is what I wanted.

Can u tell me how to do reconfiguration PLL speed using mif ?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

For PLL reconfiguration using mif , you may want to refer to AN454. I attached here for your usage. Figure 7 on page 12 of AN454 might have explanation on how you can put the mifs into each RAMs and call the mifs when you want to perform PLL reconfig.

I also attached Stratix IV design example, it might be old ref design, but it will give you an idea on how to do the PLL reconfig from multiple mifs.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Min Joo,

Based on our conversation on phone, we do believed that this is simulation model issue for VCS. I am checking on modelsim if this can be done correctly. While checking this, I will file bug report to model owner so they can fix this.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

We do not receive any response from you to the previous question/reply/answer that I have provided. This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

regards,

Farabi

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

HI ,

Generation is DONE, Synthesis is DONE,

but I can't PLL output speed with verdi simulator.

that is why I try to find out how to generate .

still can't do that

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page