Hello,

I'm running Quartus 22.3 building for an S10 FPGA.

Since my FPGA is prototype, the project includes several clock gated

to solve it I added the following command to the QSF :

set_global_assignment -name SYNTH_GATED_CLOCK_CONVERSION ON -

(replace all the clock gated to clock enable)

After the synthesis and P & R the *.syn.rpt file show list of gated clocks which found and converted to use as clock enable

but at least 1 clock gated doesn't convert and I get hold violation on this path.

I expected to see any information about this clock gated on the report like as list of unconverted gated clocks(and reason why its not converted) , but there is no list at all in this file .

please advice

連結已複製

Hi

Original code is ASIC RTL who use clock gate to decrease power supply.

Here the clock gated code:

// Gated Clock Latch

module gcw__ckltchand (

TE,

E,

CP,

Q

);

input TE;

input E;

input CP;

output Q;

wire EN_TE;

reg CPEN;

or or1 (EN_TE,E,TE);

always @(EN_TE or CP)

if(~CP) CPEN <= EN_TE;

and an1 (Q,CPEN,CP);

endmodule //gcw__ckltchand

By adding the top.v file with attached code. The tool able to recognize the gated clock and converted to use clock enables.

Info(19019): Convert gated clock gcw__ckltchand_1|Q

module top (

input i_rst_n,

input i_en,

input i_clk,

input i_data,

output reg o_data

);

wire gclk;

gcw__ckltchand gcw__ckltchand_1 (

.CP(i_clk),

.E(i_en),

.TE(),

.Q(gclk)

);

always @(posedge gclk or negedge i_rst_n) begin

if (!i_rst_n) begin

o_data <= 1'b0;

end else begin

o_data <= i_data;

end

end

endmodule

Perhaps you could check your design hierarchy to see what might be going wrong.

You could also share a simple testcase .qar file (Project > Archive Project) that you expect the tool to convert the gated clock but it does not.

Regards,

Richard Tan

HI

I tried to create a simple test case which includes :

PLL - > clock gate -> counter

I have the flag :

set_global_assignment -name SYNTH_GATED_CLOCK_CONVERSION ON

But the Quartus didn't convert the clock gate ,

Do you know why ?

I attached QAR archive file of my minimal test

We noticed that we haven't received a response from you regarding the latest previous question/reply/answer, and will now transitioning your inquiry to our community support. We apologize for any inconvenience this may cause and we appreciate your understanding.

If you have any further questions or concerns, please don't hesitate to let us know.

Thank you for reaching out to us!

Best Regards,

Richard Tan

Hi

Following to you answer you use:

gcw__ckltchand gcw__ckltchand_1 (

.CP(i_clk),

.E(i_en),

.TE(),

.Q(gclk)

);

Is it Altera primitive code ?

No, "gcw__ckltchand" is the module instantiation that you provided in your previous post. Posted on 18th April.

// Gated Clock Latch

module gcw__ckltchand (

TE,

E,

CP,

Q

);

input TE;

input E;

input CP;

output Q;

wire EN_TE;

reg CPEN;

or or1 (EN_TE,E,TE);

always @(EN_TE or CP)

if(~CP) CPEN <= EN_TE;

and an1 (Q,CPEN,CP);

endmodule //gcw__ckltchand

Hi

I found the issue,

My design includes two clock gates in a row. When I remove the second clock gate, Quartus successfully convert the first clock gate.

Why does this happen? Is there any option to resolve it?

Bu the way, the message from Quartus is unclear in understanding the issue:

Reason not converted :

Found unsupported gate top|cnvr|cnvr_tlgc_inst|cnvr_scu_ins|cnvr_scu_seq_ins|block_gated_clk_seq_ins|stdc__clk_enable_nlt_reg|gcw__ckltchand|CPEN in the gated clock tree

I replaced my clock gate instance to:

gcw__ckltchand gcw__ckltchand_1 (

.CP(i_clk),

.E(i_en),

.TE(),

.Q(gclk)

);

then I re-run synthesis and get the message:

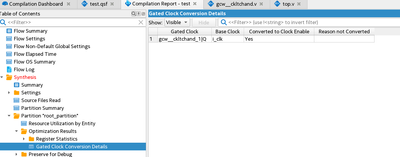

Gated clock:

top|cnvr|cnvr_tlgc_inst|cnvr_scu_ins|cnvr_scu_dig_cgu_ins|scu_top_cg_aux_clk_ins|cell__clk_enable_nlt_reg|gcw__ckltchand|an1

Base clock :

top|cnvr_pll1_inst|iopll_0|stratix10_altera_iopll_i|outclk[0]

Converted to Clock enable :

No

Reason not converted :

Found unsupported gate top|cnvr|cnvr_tlgc_inst|cnvr_scu_ins|cnvr_scu_seq_ins|block_gated_clk_seq_ins|stdc__clk_enable_nlt_reg|gcw__ckltchand|CPEN in the gated clock tree

Could you explain why Quartus did not succeed to converted?