- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hello,

i am trying to use QSPI controller along with ALTPLL. But during compilation it gives an error. Am using pll configuration with 2 clocks C0 and C1.

the error message is:

Error (176394): Can't fit 2 PLLs in the device -- only 1 PLLs are available

Info (176395): Location PLL_3 cannot be used due to package or device migration constraints

Info (176395): Location PLL_4 cannot be used due to package or device migration constraints

Info (176395): Location PLL_2 cannot be used due to package or device migration constraints

can someone please suggest how to overcome the error

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

I have not modified the design which you have shared in previous post attachments.

- You can add Qspi and PLL in Qsys system(onchip.qsys/onchip.qip) and remove the pll.qip file from project and onchip.qip set as top level entity and compile. Attached the file do pin assignment and other configuration as per you requriment

For RSU design example (QSPI &PLL) look into design stores or follow an741 or check below video links

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an741.pdf

https://fpgacloud.intel.com/devstore/platform/?search=RSU&acds_version=any&family=max-10search for reference design.

https://www.youtube.com/watch?v=Qgwd8ftiTZc

https://www.youtube.com/watch?v=bAyqWWm1yLU

https://www.youtube.com/watch?v=r3wcgr3LmjA

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

Lien copié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hello,

A single pll can have multiple outputs depending on the frequencies you want to generate. Did you consider this option?

Br.

Johi.

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

Can i know which FPGA device(P/N) are you using?

This error say it all, your device support only 1 PLL but you are using 2 PLL.

To solve you can follow the suggestion given by @JOHI or change the device as per design requirement.

Please check below thread with similar issues which may help you.

https://forums.intel.com/s/question/0D50P00003yyTYJSA2/max-10-using-two-altpll?language=en_US

Regards

ARS

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

thanks for the reply

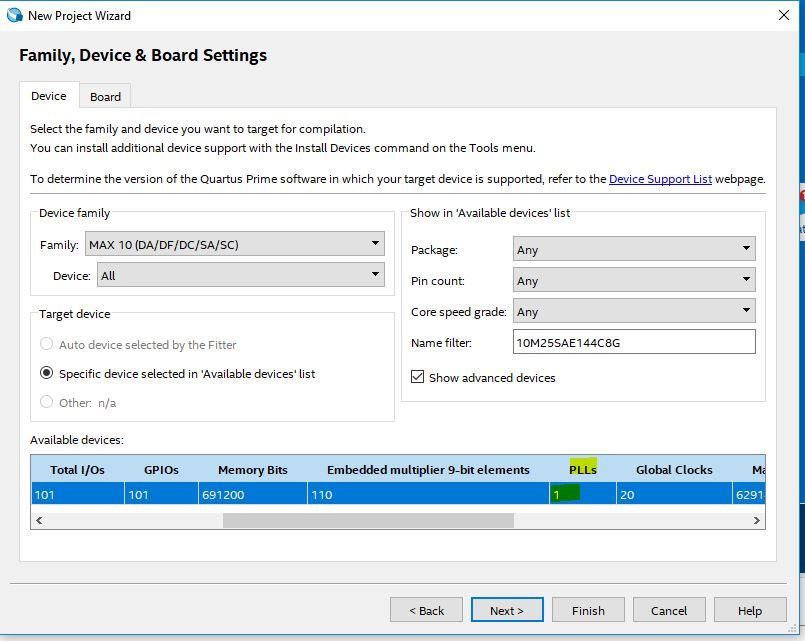

am using 10M25SAE144C8G device. it shows a resource count of 4

I can't change the device. is there any other option....

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi AKAYA,

The device 10M25SAE144C8G is having only 1 PLL.Please check the image.

You can follow the suggestion given by @JOHI , use single PLL with multiple outputs depending frequency requirement.

Regards

Anand

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

thanks for the reply...

but can you tell me what exactly is the reason for the error...

I have used an ALTPLL IP with C0 as the compensated output....

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi Akaya,

Fitter cannot place the specified node at the specified location which has been disabled to drive to the clock networks because the current package does not support it, or because it cannot be used when device migration is selected.

I guess, Initial design was for some other device from same family 10M25 which had 4-PLL and you have migrated to 10M25SAE144C8G which is having only 1 PLL because of which you are having error.

If you are using 10M25SAE144C8G device you can have 1-pll with 4-output max.

Check .qsf file for lines like set_location_assignment PLL_{number} -to "{path}"

set_location_assignment PLL_0 -to "{path}"

set_location_assignment PLL_1 -to "{path}"

set_location_assignment PLL_2-to "{path}"

set_location_assignment PLL_3 -to "{path}"

have set_location_assignment PLL_0 -to "{path}" and remove other line set_location_assignment PLL_1/2/3 -to "{path}" and Delete db and incremental_db folders and recompile the design and check.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards,

Anand

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

thank you for the reply....

I didn't change the device, am using the same device..

in the .qsf file does not contain any line like set_location_assignment PLL_{number}

can someone suggest me how to solve this

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Can you share the project?

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

thanks for the reply....

I am attaching the project here...

the QSYS is in the folder RSU--> OnChip.qsys

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

- You have to delete the db and incremental_db folders and regenerate qsys and mega-wizard pll system and recompile the design and check.

I got your project, i have just followed above steps which solves the issue and Attached project for your reference. i have used quartus 17.0 std.

If you are still facing problem use latest version of quartus tool.

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

thanks for the reply....

but the qsys file des not contain any ALTPLL or QSPI Controller....

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Duplicate

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Duplicate

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

Hi,

I have not modified the design which you have shared in previous post attachments.

- You can add Qspi and PLL in Qsys system(onchip.qsys/onchip.qip) and remove the pll.qip file from project and onchip.qip set as top level entity and compile. Attached the file do pin assignment and other configuration as per you requriment

For RSU design example (QSPI &PLL) look into design stores or follow an741 or check below video links

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/an/an741.pdf

https://fpgacloud.intel.com/devstore/platform/?search=RSU&acds_version=any&family=max-10search for reference design.

https://www.youtube.com/watch?v=Qgwd8ftiTZc

https://www.youtube.com/watch?v=bAyqWWm1yLU

https://www.youtube.com/watch?v=r3wcgr3LmjA

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Regards

Anand

- Marquer comme nouveau

- Marquer

- S'abonner

- Sourdine

- S'abonner au fil RSS

- Surligner

- Imprimer

- Signaler un contenu inapproprié

thank you for the reply....

the project is compiling now without any error...

thanks for the help

- S'abonner au fil RSS

- Marquer le sujet comme nouveau

- Marquer le sujet comme lu

- Placer ce Sujet en tête de liste pour l'utilisateur actuel

- Marquer

- S'abonner

- Page imprimable