- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi guys,

I converted two SOF files,that is the factory.sof and the application.sof to fac_app.jic file.The SOF of factory image is put in EPCS128 at start address 0,and the sof of application image is put at start address 300000h.When I burned the fac_app.jic into the FLASH and reboot,it worked well and jumped to the application image from factory image.

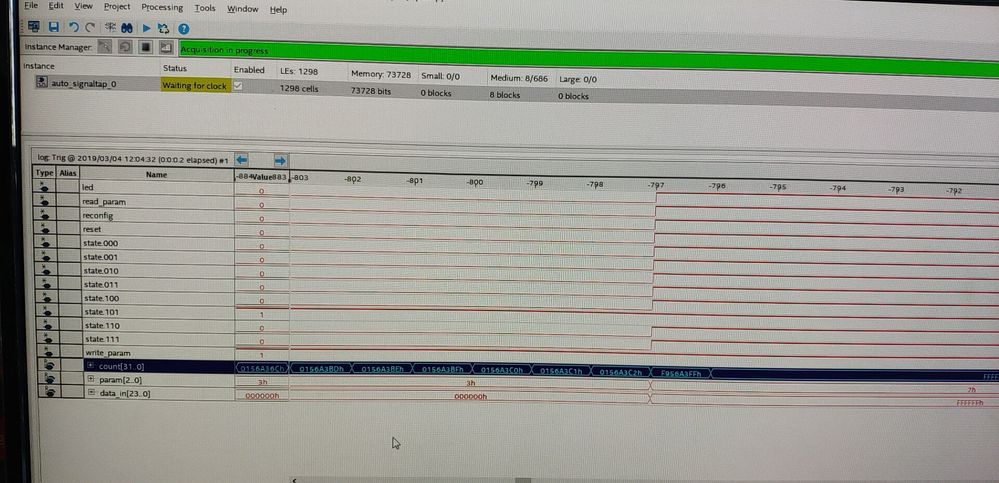

But there was something wrong when I tried to burn the BIN file of application image incompletely from burning logic of application image and reboot.My jump logic was that try to load the application image just once and stay in the factory image if it fails, then waiting for burning the BIN file form burning logic of factory image .But it failed to wait silently after a failed to load the incomplete application image that I burned deliberately.A strange phenomenon has appeared,it seems to be loading the program over and over again. When I used SignalTap II logic analyzer to observe signals that added in,the signal periodically changed from a normal state to an abnormal state of all high level as below.

Could any one tell me something about this ?By the way, I used Altera Remote Update IP Core.Thank in advance!

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi zcao0,

My recommendation is try to enable the Altera Remote Update IP parameter “Enable reconfig POF checking”. I think, it might help.

Let us know if it work or not.

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page