- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

In addition to previous comment I like to mention that the RTL viewer error in the Mux 4to2 encoder probably is at the Equal0 symbol that has 4'h1 for marking which if I'm not mistaken should be 4'h8 instead? I do not know if these errors are patched after the upgrade is done but sadly the upgrade can't be downloaded without the already installed Quartus 13.1 edition connected to the internet. Why I need an offline upgrade

package to install over my not internet connected Quartus installed computer.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Please upgrade the design to the latest version of the Intel Quartus Prime Lite edition software as some of the bugs in the older version are fixed in the later version. You may download the latest software using another internet connected PC and install in your current PC.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you KhaiY, but I can't do that because I need my Quartus II 13.1 version because of still supporting the older Spartan 3 FPGA's. Yesterday I was not being able to download the upgrade files for version 13.1 because they seemed hidden somehow.

But today the download links to both upgrade files (930MB and 407.8MB) worked, so it seems that the upgrade is going to work now. And I hope that it will remove the RTL schematic bug where "1000" is seen as 4'h1 instead of 4'h8 in the Equation symbols.

Thanks!

PS: after upgrade and a first test the error is fixed GREAT!

I however still found a strange RTL result in an Excess3 converter.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

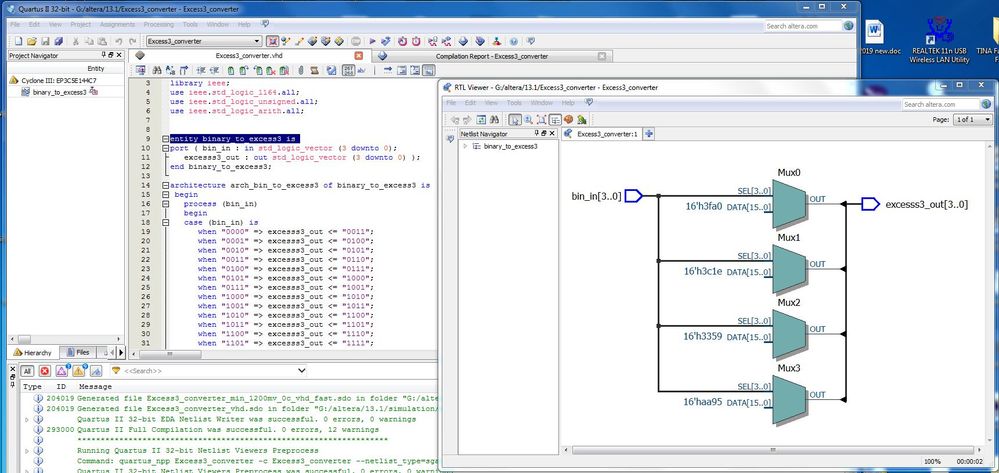

Above

Above the strange 16bit results in the 4 muxes in the RTL viewer Excess3 converter window. In the program code 4 bits wide is the highest declared. What is wrong here? Is it another bug in the RTL viewer, or has it to do with taking the negative 2 complement and adding 9's to get the positive Excess3 equivalent value?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you provide the design.qar for investigation? I can help to test on my side.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Okay. Hereby I'll try to attach that qar file. If nothing is wrong in my RTL viewer, I like to understand what those 16'hex numbers represent. I suppose that I need to limit the possible terms in Karnaugh to get those results?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You may create the design.qar by clicking on Project > Archive Project > Archive

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Upon checking, the schematic in RTL VIewer with Synthesis rtl dump file are the same, there is no mismatch in the result. Have you tried simulate the design to check the functionality?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY, this problem was already solved in the past by upgrading my buggy 13.1 Quartus II version. I did however leave another answer on the Forum that was another problem. I add it below. And I think it is caused by differences in the FPGA structures and/or differences between the VHDL designers from Quartus and Xilinx:

- Quartus II 13.1 (upgraded) fails terribly where Xilinx produces perfect RTL schematics from the same VHDL code! And I already upgraded Quartus to get rid of the wrong terrible bugs that showed in its RTL results. And the Intel site gave none help, no support to ask a question by sending a simple email sadly!

- See next code that after days of wasted checking keeps failing in Quartus but works great as it is in Xilinx ISE 14.6!

- HELP !!! QUARTUS II Web free version 13.1 (32-bit) for Windows 7 fails many times to compile a perfectly good VHDL example code!

- Those examples tried never work in Quartus but the same files

- WORK PERFECTLY in Xilinx ISE version 14.6 !!! (on a Windows XP laptop).

- See following VHDL code below of an UpCounter that never works in Quartus II for some reason but works great in Xilinx ISE producing a decent and correct RTL schematic!

- ----------------

- -- Engineer: Albert van Bemmelen

- -- Create Date: 15:46:31 05/09/2020

- -- Module Name: UpCounter - Behavioral

- -- Upcounter Vahid book

- library ieee;

- use ieee.std_logic_1164.all;

- entity UpCounter is

- port ( clk: in std_logic;

- cnt: in std_logic;

- C: out std_logic_vector(3 downto 0);

- tc: out std_logic);

- end UpCounter;

- architecture structure of UpCounter is

- component Reg4

- port ( I: in std_logic_vector(3 downto 0);

- Q: out std_logic_vector(3 downto 0);

- clk, ld: in std_logic);

- end component;

- component Inc4

- port ( a: in std_logic_vector(3 downto 0);

- s: out std_logic_vector(3 downto 0));

- end component;

- component And_4

- port ( w,x,y,z: in std_logic;

- F: out std_logic);

- end component;

- signal tempC: std_logic_vector (3 downto 0);

- signal incC: std_logic_vector(3 downto 0);

- begin

- Reg4_1: Reg4 port map(incC, tempC, clk, cnt);

- Inc4_1: Inc4 port map(tempC, incC);

- And_4_1: And_4 port map(tempC(3),tempC(2),tempC(1),tempC(0), tc);

- outputC: process(tempC)

- begin

- C <= tempC;

- end process;

- end structure;

- I am trying to understand why Quartus makes a problem of good VHDL code where it shouldn't be!!

- Any help is greatly appreciated!

- Albert van Bemmelen

- Weert The Netherlands.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Have you tried to compile in the latest version of the software, which is 19.1 as some of the bugs in the older version were fixed in the newer version?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No sadly for not being able to install the 64 bit versions on old laptops or old windows 7 and earlier versions. And because I need to work with my Digilent Spartan 3E experimenter's board. And I use my only online Windows 10 laptop for safe online action only.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

You mentioned that this problem was already solved in the past by upgrading the 13.1 Quartus II version. May I know what is the version that you did not see the error?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

The Quartus version I use on my Windows 7 desktop is Quartus II 32-bit version 13.1.4 Build 182 03/12/2014 SJ Web Edition. And is the version that failed to compile above example and others where Xilinx Ise 14.6 had no problem with to create the right RTL circuits.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

So above mentioned Quartus not compiling where Xilinx ISE perefectly compiles is a new problem that was not solved yet. Only a previously noticed wrong marking error/bug in the RTL presentation was solved after upgrading to present version.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

And below is another example of VHDL code that perfectly works in Xilinx ISE (not Spartan3E but with higher FPGA's only!) but never works in Quartus:

--BRAM_16x2 page194 Vaibbhav Taraate.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity BRAM_16x2 is

port (q_out : out std_logic_vector (1 downto 0);

write_en : in std_logic;

clk: in std_logic;

d_in: in std_logic_vector (1 downto 0);

a_in: in std_logic_vector (3 downto 0));

end BRAM_16x2;

architecture BRAM_arch of BRAM_16x2 is

component BRAM_16x1S is

port(O : out std_logic;

D: in std_logic;

A3, A2, A1, A0: in std_logic;

WE, W_CLK: in std_logic);

end component;

begin

U0: BRAM_16x1S port map (O =>q_out(0), WE =>write_en, W_CLK =>clk, D =>d_in(0),

A0 =>a_in(0), A1 =>a_in(1), A2 =>a_in(2), A3 =>a_in(3));

U1: BRAM_16x1S port map (O =>q_out(1), WE => write_en, W_CLK => clk, D =>d_in(1),

A0 =>a_in(0), A1 =>a_in(1), A2 =>a_in(2), A3 =>a_in(3));

end BRAM_arch;

--------------Which gives following error rapport in Quartus II 13.1 but works in ISE! -------

Warning (20028): Parallel compilation is not licensed and has been disabled

Warning (12125): Using design file bram_16x2.vhd, which is not specified as a design file for the current project, but contains definitions for 2 design units and 1 entities in project

Info (12022): Found design unit 1: BRAM_16x2-BRAM_arch

Info (12023): Found entity 1: BRAM_16x2

Error (12006): Node instance "U0" instantiates undefined entity "BRAM_16x1S"

Error (12006): Node instance "U1" instantiates undefined entity "BRAM_16x1S"

Error: Quartus II 32-bit Analysis & Synthesis was unsuccessful. 2 errors, 2 warnings

Error: Peak virtual memory: 393 megabytes

Error: Processing ended: Mon May 11 17:13:47 2020

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:02

Error (293001): Quartus II Full Compilation was unsuccessful. 4 errors, 2 warnings

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I understand that the original RTL mismatch problem is solved by upgrading the software to Quartus II 32-bit version 13.1.4 Build 182 03/12/2014 SJ Web Edition.

For the new error below, can you share the full design.QAR file for investigation? To create the design, click on Project > Archive Project > Archive

Error (12006): Node instance "U0" instantiates undefined entity "BRAM_16x1S"

Error (12006): Node instance "U1" instantiates undefined entity "BRAM_16x1S"

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you have any updates?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

No sadly I have just quit for the time being unable to solve the Quartus II issues presented above. I also use Xilinx that works where Quartus completely failed in the given examples. And another problem arose that made me get stuck in my Quartus II version in that it apparently doesn't automatically use the simulation testfile that was made for a 4 to 1 Mux and its already in the VHDL file put in In- and output declarations and the to simulate input data. It apparently never is intuitive which would make starting to use Quartus much easier. Never knowing (all off-line without on-line connection) how to use Quartus II correctly. Apparently I still have to manually set all input and outputs before any simulation is possible in Quartus? I keep reading books on VHDL , the best one yet was Vaibbhav Taraate's PLD Based Design with VHDL, but still I need another book on how to use Quartus. (the BRAM examples and other examples from that book failed in Quartus but worked in Xilinx ISE!). So at the moment I just keep on reading other books on VHDL too and didn't get any further where Quartus is concerned.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Do you still see the error below? If yes, can you provide the design.qar for investigation?

Error (12006): Node instance "U0" instantiates undefined entity "BRAM_16x1S"

Error (12006): Node instance "U1" instantiates undefined entity "BRAM_16x1S"

For the new question on simulation: It apparently doesn't automatically use the simulation testfile that was made for a 4 to 1 Mux and its already in the VHDL file put in In- and output declarations and the to simulate input data. can you open a new forum post to make sure that there is only one question in one post? This helps to reduce confusion to the other users who have the same error and helps them to find the solution to each of the error/question easily.

Thanks.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page