- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- « Previous

-

- 1

- 2

- Next »

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

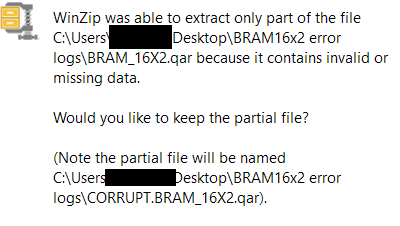

The rar file is corrupted. Could you reattach?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Albert,

Can you send the entire project directory in ZIP?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Albert,

In the .map.rpt file you have attached, there are two error messages:

Error (12006): Node instance "U0" instantiates undefined entity "BRAM_16x1S" File: J:/altera/13.1/bram_16x2.vhd Line: 46

Error (12006): Node instance "U1" instantiates undefined entity "BRAM_16x1S" File: J:/altera/13.1/bram_16x2.vhd Line: 49

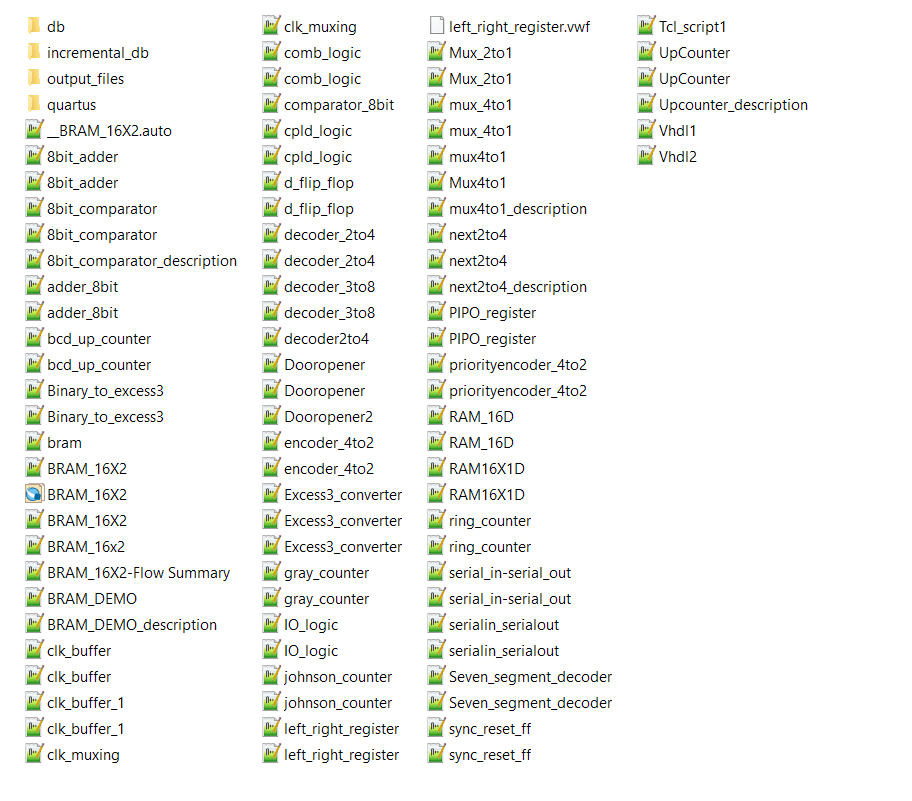

The error indicates that the BRAM_16x1S HDL file is not added to the Project. I compile the qar file, there is no BRAM_16x1S file in the project directory. Can you check if you have add this file to the project? You may check from the Project Navigator.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY, the vhdl file contains a component named BRAM_16x1S as part of the archive BRAM16x2 archtecture. It works splendidly as it is in Xilinx ISE 14.6. But Quartus 13.x fails to compile this same vhdl file. This is that file:

----------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 22:57:22 05/09/2020

-- Design Name:

-- Module Name: BRAM_16x2 - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

----------------------------------------------------------------------------------

--BRAM_16x2 blz.194

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity BRAM_16x2 is

port (q_out : out std_logic_vector (1 downto 0);

write_en : in std_logic;

clk: in std_logic;

d_in: in std_logic_vector (1 downto 0);

a_in: in std_logic_vector (3 downto 0));

end BRAM_16x2;

architecture BRAM_arch of BRAM_16x2 is

component BRAM_16x1S is

port(O : out std_logic;

D: in std_logic;

A3, A2, A1, A0: in std_logic;

WE, W_CLK: in std_logic);

end component;

begin

U0: BRAM_16x1S port map (O =>q_out(0), WE =>write_en, W_CLK =>clk, D =>d_in(0),

A0 =>a_in(0), A1 =>a_in(1), A2 =>a_in(2), A3 =>a_in(3));

U1: BRAM_16x1S port map (O =>q_out(1), WE => write_en, W_CLK => clk, D =>d_in(1),

A0 =>a_in(0), A1 =>a_in(1), A2 =>a_in(2), A3 =>a_in(3));

end BRAM_arch;

-------------------------------

I'll add it hereby as attachement too.

Thanks again for taking the time to look into the problem!

Albert.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Albert,

The BRAM_16x2vhd is instantiating the BRAM_16x1S but there is no BRAM_16x1S HDL file in the archive.

Could you provide BRAM_16x1S ?

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi KhaiY, that is the problem, why it probably isn't working in Quartus II. But this file as it is, works splendidly in Xilinx ISE 14.6 without any problem! That is why I asked this question. I just noticed that it only works in Xilinx ISE 14.6 when a higher type FPGA is chosen. Earlier Xilinx FPGA's probably were unable to work as BRAM configurated FPGA's.

Because a Xilinx Spartan 3E failed to compile this BRAM file that works splendidly on a Xilinx Zynq XA 7z010 FPGA as it was given in the above mentioned BRAM_16x2 vhdl file from the book : PLD BASED DESIGN WITH VHDL by Vaibbhav Taraate.

I know too little yet about the Quartus II and Xilinx ISE programs to know why the file creates problems in Quartus II. But I guess it has to do with what version of program is used.

Thanks!

Albert.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Albert,

I appreciate your explanation on the issue, but unfortunately we are not in liberty to discuss on our FPGA software especially in comparison to our competitor products.

I am happy to address the implementation challenges that is related to our FPGA software. In general, all the source files need to be added to the project directory for successful compilation. In this case, the software reports that the source file for BRAM_16x1S is missing in the project directory. You have to add the source file for this BRAM_16x1S if you want to instantiate it in the bram_16x2.vhd file.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Understood KhaiY. But since the current file worked in Xilinx without the BRAM_16x1S file, it wasn't needed and therefore not given in the mentioned book. And if I had that file I wouldn't know how to add it to the project anyhow. Especially if it can't be added to the existing vhdl file. I already tried to do that previously to get it compiled in Quartus until I found out that it already worked in its present version in Xilinx ISE 14.6.

Thanks.

Best regards.

Albert.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Albert,

In the Intel Quartus Prime software, you have to add the logic design files that contain the logic that implements your design into the Project. The source file can be in HDL(.v/.vhd/.sv), Verilog Quartus Mapping (.vqm) design files and Platform Designer (Standard) system (.qsys). It this case, it is not possible to instantiate BRAM_16x1S without the source file that describes how BRAM_16x1S works in the design.

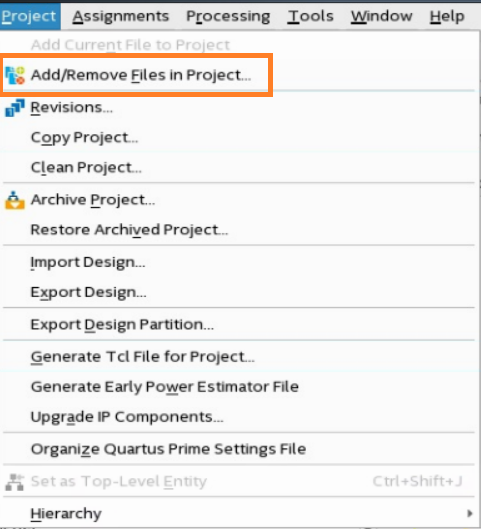

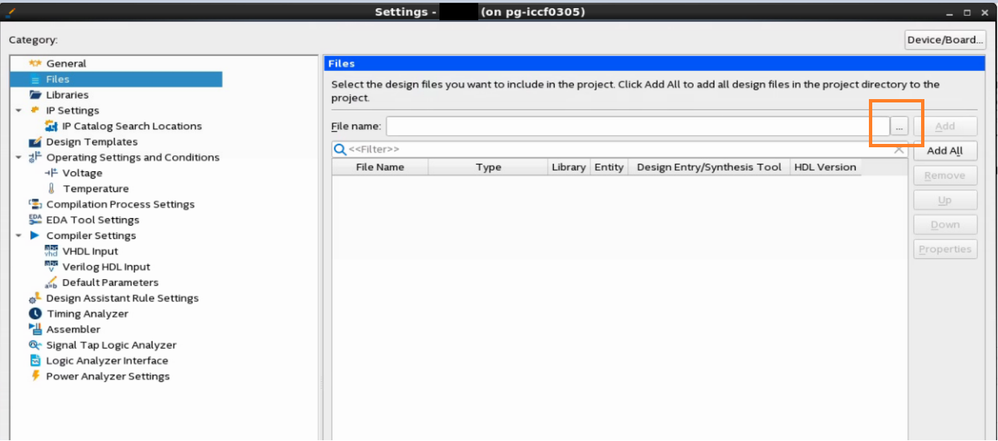

To add the files into the Project

1) Click on Project > Add/Remove Files in Project

2) Click on ... icon to add the files

3) Ok

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks KhaiY, I will try your much appreciated explanation later on today when I'm back from my job. I hope that I will manage to get the BRAM file running in Quartus this time.

Have a great day!

Albert.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Albert,

Sure. Do let me know if you have any questions.

Thanks.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Albert,

Do you have any other questions? If no, I shall transition this thread to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

Best regards,

KhaiY

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Albert,

Sure. You are welcome to open a new forum thread if you need help in the future.

Thanks.

Best regards,

KhaiY

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

- « Previous

-

- 1

- 2

- Next »