- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I would recommend to use Modelsim for your simulation as I able to do so without error.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello, thanks for helping me.

I am not using Modelsim yet.

So I use Simulation Waveform Editor.

I did the simulation again in the Simulation Waveform Editor today, but the error message opens like the attached picture.

I hope you simulate it in the Simulation Waveform Editor.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have request the engineering team to look into this whether this error message can be suppressed or configure the setting.

May I know which Quartus version are you using?

Fyi, you can download and learn to use our ModelSim*-Intel® FPGA Edition tool in our https://fpgasoftware.intel.com webpage.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

You need to convert your many BDFs to Verilog or VHDL. Open your BDF in the GUI, then go to File->create/update->create hdl design file for current file. You can select Verilog or VHDL.

For your simulation waveform editor, you can convert it to Modelsim testbench. Open your vwf in the GUI, then go to simulation -> Generate Modelsim Teshbench and script.

With verilog/vhdl file and testbench, you basically can start to simulate using Modelsim.

You can refer to this document on how to simulate using Modelsim:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_gs_msa_qii.pdf

There is also a list of document related to simulation using different simulator and Quartus Pro/std version in the link below:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

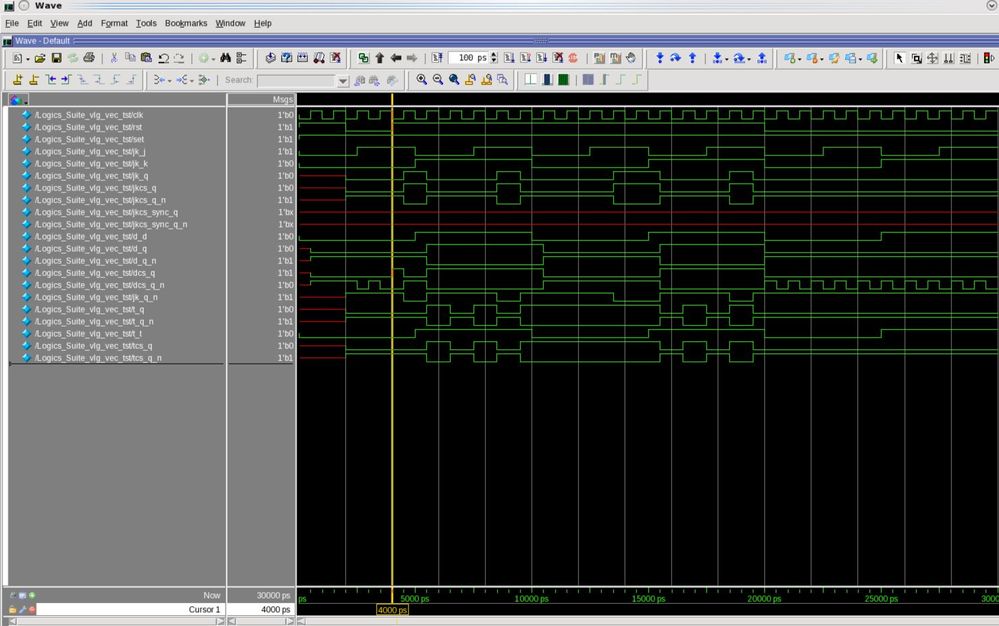

I try to set the Iteration limit to 10_000_000 and the simulation still fails in the Simulation Waveform Editor at 4 ns when the reset signal assert from low to high.

There might be zero-delay loops that exist in your design. Two common causes are a loop that has no exit, or a series of gates with zero delays where the outputs are connected back to the inputs.

vsim Message # 3601:

# The simulator iterates at a given simulation time in zero delay until

# there is no more activity at that time. In order for it to not hang if

# there is a zero-delay oscillation, it limits the number of iterations

# to a default of 10 million. If you reach this limit, the simulation will stop

# with an error. If you receive this error you can increase the iteration

# limit, (via "set IterationLimit <newvalue>") and then try single

# stepping to attempt to determine which instances in the design may be

# oscillating or run the simulation again with -iterationlimit=f and/or +autofindloop.

# [DOC: ModelSim User's Manual - Detecting infinite zero-delay loops]

#

# This error message can be suppressed or downgraded to a note or warning.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page