- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We have a design where we control an external RAM memory. We generate the CLK and control memory signals in a FPGA (Cyclone IV). The CLK signal is generated using a PLL, with 180º phase shift.

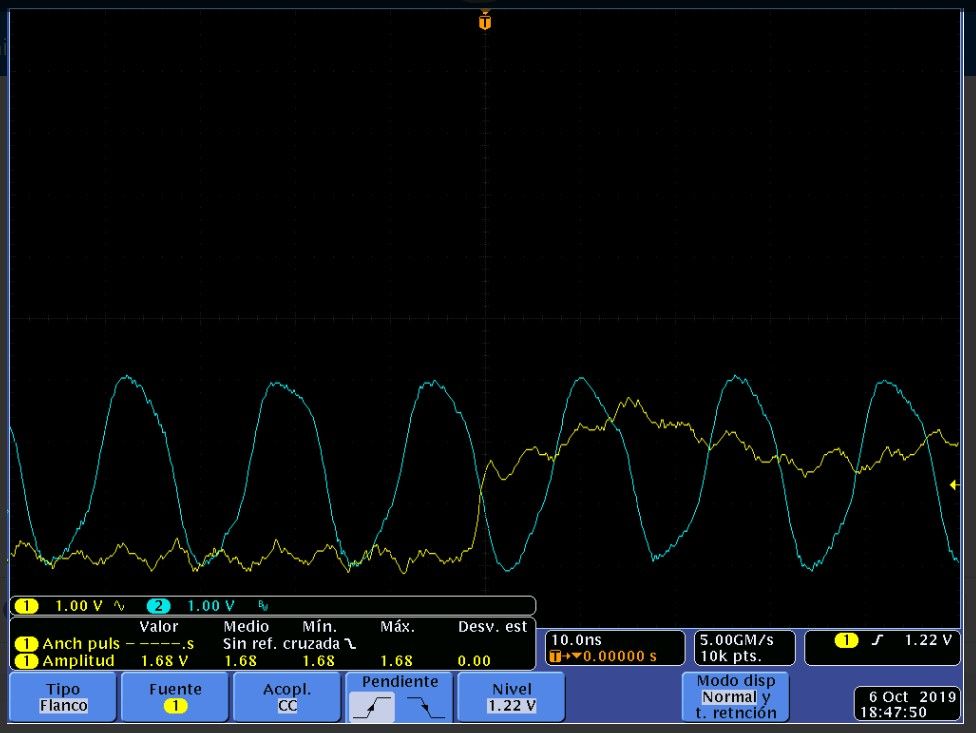

The design is working but we have detected that "set_output_delay" dosen't apply. For example, we have compared, in an oscilloscope, the delay beetwen the signals CLK and a bit ADD[15] bus and it is constant for any "set_out_delay".

We are using the next constrains configuration:

create_clock -name RAM_CLK -period 16 [get_ports {RAM_CLK}]

create_generated_clock -name vt_RAM_CLK -source [get_ports {RAM_CLK}] -divide_by 1 -multiply_by 1 -phase 180

set_output_delay -clock {vt_RAM_CLK} 3 [get_ports {RAM_ADD[15] }].

In next figure, you can see timing of both signals.

The delay is contant for any "output_delay" value (0, 1, 2, 3..).

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

What is the max and min output delay? Is it within range?

Can you report Ignored Constraints and see if the set_output_delay constraint is being ignored?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your email.

The constraints are not included in ignored constraints report.

We tried with delay between 0 to 8. With the same and different max / min values.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Does the delay exceed the max/min value specified?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The phisical delay beetwen both signals is always the same, about 0ns

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know the software version and edition? Can you share the test case for investigation?

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

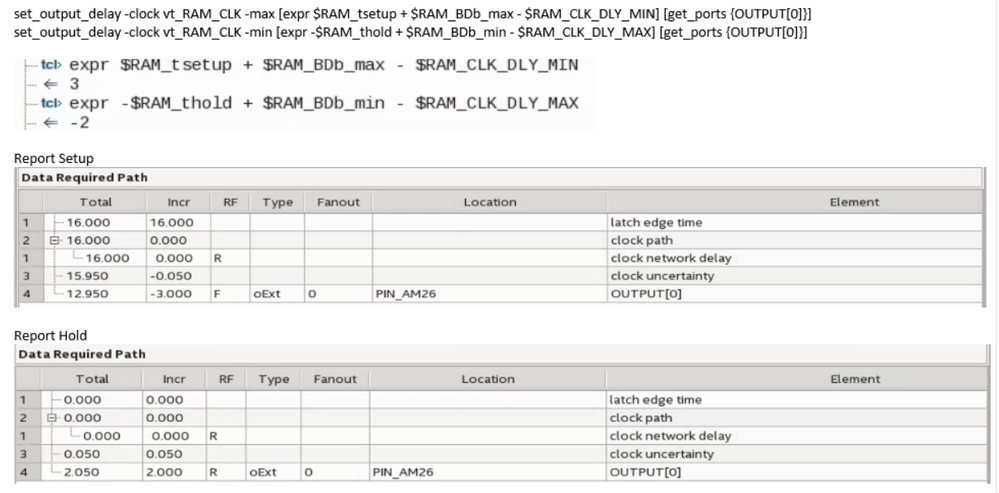

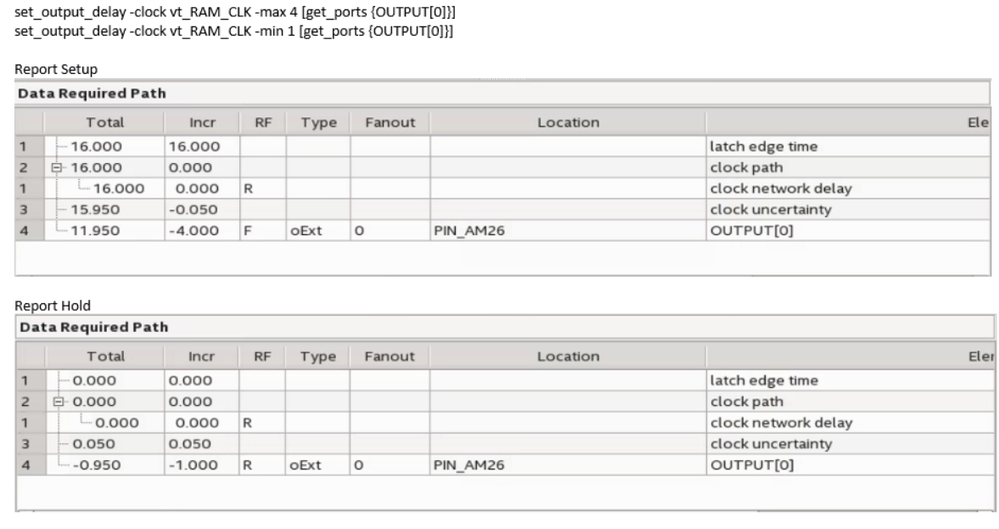

I check the project.qar, the output delay is the same as the value in the .sdc file

Example 1:

Example 2:

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks for your email.

I know that the delay in the Timequest simulation is correct, probably I forgot to comment it. The problema is I dont see this delay monitoring the signal in the oscilloscope.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is the measured delay is within the range set in the sdc?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The delay is always the same.

Can you test the output signals in a test board o similar?

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I understand that the delay is the same. Does the delay exceed the delay set in the sdc? The result in the timing analysis is the worst case scenario. Just would like to make sure that the delay measured is within the range.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The phisical delay lower to the max/min delay setting.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Is the signal being captured correctly at the receiver end?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In the real design, we use a phase 190º shift clock and is it working. For the test, we are using a 0º phase shift clock, and is also working even without any constraints.

Anyway, it is strange for me, the timing in the oscilloscope of both signals (data and clock) are the same for any "output_delay value" (form o to 12n for example). In some of them Time quest reports setup error.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Where do you probe the signal?

Referring to Figure 10 in https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl_timequest_cookbook.pdf, do you probe at the data_out of the FPGA or data_in of the external device?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Our design is different to figure 10 architecture. We generate the CLOCK in a FPGA PLL. You can see more details in my first message. The FPGA and the memory are very near, and I have connected both probes near memory pins.

For example, the inpout delay setting ir working properly. The design includes 16 LVDS DDR channels and 4GHz, and if I modify the setting to a wrong value we get wrong data.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know what do you mean by wrong value settings?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

I want to say values out of range of Inputs requirements.

Regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It is expected for the receiver end to receive the wrong data if the value set is out of the range of the input requirement.You have to make sure that the value set is with the input requirement of the receiver end.

Please let me know if I understand wrongly. There is no timing violation reported in the Timing Analysis and the signal is being captured correctly at the reciever end when the delay is set within the range of input requirement.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It seems I have not explain correctly.

In the input case, the setting is defined correctly the setting, but I modified it to a wrong value to confirm that the constraints apply as it was expected.

In reference to the output setting, it is also working properly but I want to test that I'am able to modified the CLK-signal timing using a wide range of max/min (from 0 to 12 for example) "output_delay". But the real delay is the same.

Regards

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page