- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm using an Altera Cyclone II DE2 version from my university.

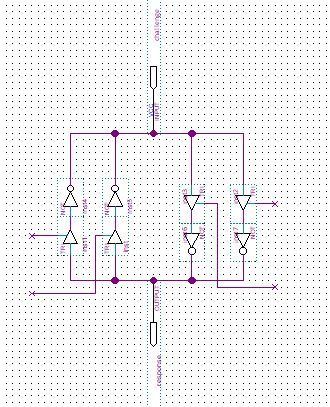

I'm don't seem to be able to find the components illustrated in Fig. 11 and how I should read Fig. 10.

Any explanations or references would be greatly appreciated, as I'm quite new to the world of FPGAs.

Thank you in advance,

Best regards.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

"Any explanations or references would be greatly appreciated, as I'm quite new to the world of FPGAs."

May I know the following things, please ?

- what exactly you are trying to do.

- How it is related to Altera Cyclone II DE2

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm working on a research project in which I would implement the shown design, which is a variation of a cyber-physical security device called the Physically Unclonable Function (PUF), and later perform a security analysis on it.

Throughout the literature, the design has been implemented on FPGAs, and given that my university already possesses a Cyclone II DE2, they lent one to me to implement the shown design.

My issue is that it requires both knowledge of manual place & routing and the design of its fundamental gate, which is a tristate inverter, but I'm unable to do either because I'm quite novice in the world of FPGAs and that I'm not able to read the figures the image I provided.

Your help is highly appreciated,

Thank you in advance,

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

Does the Altera Cyclone II DE2 have an internal tristate inverter? If so then how can I use it in my design? And if not then how should I go about making a tristate inverter component in Quartus II?

Thank you in advance,

Best Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Greetings,

I'm very looking forward for a reply if you please, I hope you can help me. The research paper posted above gave me no additional knowledge outside the design I already attached and presented in my original question. So if someone could aid me to access the tristate inverters in the Cyclone II DE2 it would be greatly appreciated.

Thank you in advance,

Best regards to all.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

"The research paper posted above gave me no additional knowledge outside the design I already attached and presented in my original question."

Have you gone through it seriously?

Check the TRISTATE INVERTER : FIGURE 6: A tristate inverter. And TSRAM PUF : FIGURE 7: An 1-bit TSRAM PUF. and relative explanation.

Go through it again until you clearly understand.

Then refer the below link & try by yourself with quartus tool,

ftp://ftp.altera.com/up/pub/Tutorials/DE2/Digital_Logic/tut_quartus_intro_schem.pdf

Let me know if this has helped resolve the issue you are facing or if you need any further assistance.

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I don't think tri-state inverters are there in Cyclone II devices, there may be Tristate buffers. You could try to implement it this way :

May need to check the placement of the tristate buffers.. its either before or after the inverter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi there Vicky and Abraham,

I've very much gone through it seriously, I've already came across the design introduction document you linked. I've also already tried multiple ways of implementing a tristate inverter, including Abraham's idea, along with an idea of creating a schematic symbol from a VHDL file and then using them to create the TSRAM PUF cell, however my primary problems remain, please allow me to explain them in detail:

1) A PUF is a device that produces an output that is the settled value of the lower or upper node of the circuit, and this value depends on the physical characteristics of the design, hence the design have to be physically symmetric in terms of the positions of the LEs used, which is where the manual place and route comes in, however, no matter how I design my PUF, the synthesizer will never pass through my component instantiations as I declared them (I even attempted to use LCELLs without success).

2) Because I'm going to replicate the PUF CELL in order to have a full multi-bit TSRAM PUF, I'm going to have to create a hard macro out of my design.

And I'm unable to find the knowledge or guidance as of how to tackle these problems.

Any help would be highly appreciated. I apologize for any inconvenience.

Thank you all in advance,

Best regards,

M. Alhaidary.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Alhaidary,

"which is where the manual place and route comes in, however, no matter how I design my PUF, the synthesizer will never pass through my component instantiations as I declared them (I even attempted to use LCELLs without success)."

It`s difficult to support without looking the design. I hope,to proceed further our suggestion might helps to you.

Best Regards

Vikas Jathar

(This message was posted on behalf of Intel Corporation)

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page

![20180921_161028[1].jpg 20180921_161028[1].jpg](/t5/image/serverpage/image-id/131iCE964327AA98B3B2/image-size/large?v=v2&px=999&whitelist-exif-data=Orientation%2CResolution%2COriginalDefaultFinalSize%2CCopyright)