- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

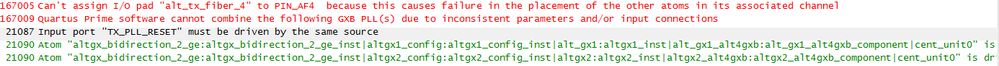

As I understand it, you observe some issue when trying to compile your design with SIV GX ALTGX with two refclk sources. Would you mind to share with me a simple test design with ALTGX which could replicate the observation so that I could further look into it? Please let me know the specific Quartus version that you are using as well. thank you.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page