- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

my program is:

module detector (s_out, s_in, reset, clk);

input s_in, reset, clk;

output s_out;

reg s_out;

reg state;

parameter even=0,odd=1;

always@(posedge clk or reset)

begin

if(reset)

state<=even;

else

case(state)

0:begin

state<=s_in?odd:even;

s_out<=s_in?1:0;

end

1:begin

state<=s_in?even:odd;

s_out<=s_in?0:1;

end

default:state<=even;

endcase

end

endmodule

but the program is not working for most test cases...help

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Could you elaborate in details? Do you mean compilation error? Could you provide the error message?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

the program question is:

It is required to implement a sequence detector that will accept a serial bit stream “s_in” in synchronism with the positive edge of a clock, and will generate a serial bit stream “s_out” as output. The next bit of “s_out” will be 1, if the number of 1’s in “s_in” seen so far is odd; it will be 0 otherwise. The state transition diagram will consist of two states indicating whether the number of 1’s seen so far is odd or even. A “reset” low signal is used to asynchronously initialize the state to the “even 1’s state”.

my program:

module detector (s_out, s_in, reset, clk);

input s_in, reset, clk;

output s_out;

reg s_out;

reg state;

parameter even=0,odd=1;

always@(posedge clk or reset)

begin

if(!reset)

state<=even;

else

case(state)

0:begin

state<=s_in?odd:even;

s_out<=s_in?1:0;

end

1:begin

state<=s_in?even:odd;

s_out<=s_in?0:1;

end

default:state<=even;

endcase

end

endmodule

result of testcases:

Compilation : Passed

Public Test Cases: 1 / 4

Test Case 1

Pass: (state = x, s_in = 0, reset = 0) => (state = 0, s_out = x, reset = 0)\n

Pass: (state = x, s_in = 0, reset = 0) => (state = 0, s_out = x, reset = 0)\n

Passed

Test Case 2

Pass: (state = 0, s_in = 1, reset = 1) => (state = 1, s_out = 1, reset = 1)\n

Fail: (state = x, s_in = 1, reset = 1) => (state != 0, s_out != x, reset != 1)\n

Wrong Answer

Test Case 3

Pass: (state = 1, s_in = 1, reset = 1) => (state = 0, s_out = 0, reset = 1)\n

Fail: (state = 0, s_in = 1, reset = 1) => (state != 1, s_out != 1, reset != 1)\n

Wrong Answer

Test Case 4

Pass: (state = 1, s_in = 0, reset = 1) => (state = 1, s_out = 1, reset = 1)\n

Fail: (state = 0, s_in = 0, reset = 1) => (state != 0, s_out != 0, reset != 1)\n

Wrong Answer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

In an Event Control in the HDL, you specified an Event Control that contains both double-edge events and single-edge events. You cannot include both event types in one Event Control.

always@(posedge clk or reset)

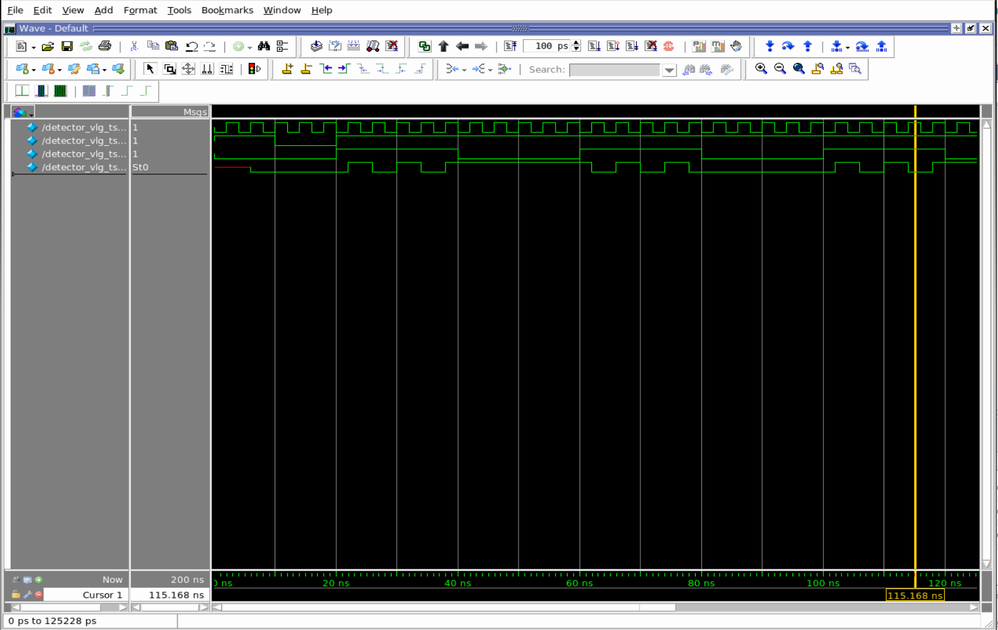

I edited the HDL and the simulation result is correct.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you Sir. I just learned something new.But even after modification,some private test cases are wrong

i will get an exact answer by tomorrow and will update the program here as soon as possible

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sure.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

module detector (s_out, s_in, reset, clk);

input s_in, reset, clk;

output s_out;

parameter EVEN=1'b0, ODD=1'b1;

reg s_out, state;

always @(posedge clk, reset)

begin

if (!reset)

state <= EVEN;

else begin

case ({state,s_in})

2'b00,2'b11: begin

s_out <= 1'b0;

state <= EVEN;

end

2'b01,2'b10: begin

s_out <= 1'b1;

state <= ODD;

end

endcase

end

end

endmodule

allthough i think its the same program in a different way!!!!!!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

any idea on how to implement this program?

Write a Verilog module to implement a 32-bit Booth’s multiplier using behavioural style. The module will take two 32-bit multiplier (“mpr”) and multiplicand (“mpd”) as inputs, and produce a 64-bit product (“prod”) as output. An active high input signal “start” is used to start the multiplication, and after completion of the multiplication, a signal “done” will be set to 1.and carry out the tasks at any individual stage including state transition in the failing edge of an input clock “clk”.

The following module template must be used for implementation:

module booth (mpr, mpd, prod, start, done, clk);

input [31:0] mpr, mpd;

input start, clk;

output [63:0] prod;

output done;

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know the status? Have you resolved the first error with the HDL code I have attached earlier?

For the second question, you may refer to a video published by Intel FPGA: Verilog HDL Basics

https://www.youtube.com/watch?v=PJGvZSlsLKs. The video shows how to implement behavioural statement at 31:02mins.

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

yes the issue was resolved.

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

the program i came up with is:

module booth (mpr, mpd, prod, start, done, clk);

input [31:0] mpr, mpd;

input start, clk;

output [63:0] prod;

output done;

integer i;

reg [31:0] A, Q, M;

reg Q_1;

reg [5:0] count;

initial

begin

A <= 32'b0;

M <= mpd;

Q <= mpr;

Q_1 <= 1'b0;

count <= 6'b100000;

end

always@(negedge clk)

begin

case ({Q[0], Q_1})

2'b00 : {A, Q, Q_1}=A<<<Q<<<Q_1;

2'b01 : begin

A=A+M;

{A, Q, Q_1}=A<<<Q<<<Q_1;

end

2'b10 : begin

A=A-M;

{A, Q, Q_1}=A<<<Q<<<Q_1;

end

2'b11:{A, Q, Q_1}=A<<<Q<<<Q_1;

endcase

count=count-1'b1;

end

assign prod = {A, Q};

assign done = (count==0);

endmodule

no compilation errors but not working for these test cases:

Compilation : Passed

Test Case 1

0

Pass: (start = 1, mpr = 16, mpd = 10) => (clock cycles = 37, prod = 160, done = 1)\n

Fail: (start = 1, mpr = 16, mpd = 10) => (clock cycles = 37, prod != X, done != 0)\n

Wrong Answer

Test Case 2

1

Pass: (start = 0, mpr = 16, mpd = 10) => (clock cycles = 37, prod = x, done = x)\n

Fail: (start = 0, mpr = 16, mpd = 10) => (clock cycles = 37, prod != X, done != 0)\n

Wrong Answer

Test Case 3

2

Pass: (start = 1, mpr = 75, mpd = 20) => (clock cycles = 41, prod = 1500, done = 1)\n

Fail: (start = 1, mpr = 75, mpd = 20) => (clock cycles = 41, prod != X, done != 0)\n

Wrong Answer

Test Case 4

3

Pass: (start = 1, mpr = 85, mpd = 60) => (clock cycles = 43, prod = 5100, done = 1)\n

Fail: (start = 1, mpr = 85, mpd = 60) => (clock cycles = 43, prod != X, done != 0)\n

Wrong Answer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

It is glad to hear that the first issue was resolved.

For the second issue, may I request the design file and simulation result?

Thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you have any updates?

Thanks.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page