- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello,

I am not an expert in semiconductors or IT industry, so I hesitate to post a question here, but please let me try.

A few days ago, I just saw news of new product Stratix 10 NX will release, which improves its computation block from DSP block to Al Tensor Block and make computing 15 times faster. When I saw a picture of its comparison, I remember the logical circuit invented last year. It is like, diode-OR circuits connected in parallel might form a combination of OR and AND as uploaded on Github.

So I am wondering if my parallel design can apply to the composite of Al Tensor Block, or simply DSP blocks are built in parallel.

Thank you,

Ryoji

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ryoji,

Thanks for your update. Sorry as I am not really familiar with low level logic design and thus could not really comment on your circuitry. Sorry for the inconvenience.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ryoji,

Thanks for contacting us. As I understand it, you seems to have some inquiries related to the latest S10 NX device. Sorry as I am not very clear on your specific inquiry. To ensure we are on the same page, would you mind to further elaborate on your specific inquiries? Just wonder if you are referring to if your design can be fitted in to the device or not?

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Chee Pin,

Thank you for your replay.

I have been thinking about how to reply to an email where your auto-reply mail is pointing. So please let me send it as soon as possible with further elaboration.

Thank you again,

Ryoji

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Just would like to follow up with you on this. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Chee Pin,

Thank you for taking the time to my question.

I heard in recent years; semiconductor materials are not only Si (Silicon) semiconductors but also GaN (gallium nitride) or SiC (silicon Carbide) ones. If we can combine these conductors in parallel, we may be able to use GaN for OR block and Si to AND block as combo gate on Fig.5 in my paper. If I practically explain more, this is an idea of how to apply my concept to existing semiconductors immediately.

So I wonder if my design can be fitted into the device or not, like this way?

And another question I have sent as an email is if it is such a new(?) and fundamental upgrade of computing architecture, is it possible to manage it under an open-source license like GNU Lesser General Public License (LGPL)?

Sincerely,

Ryoji

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ryoji,

Thanks for your update. For your information, I do not have much visibility into the semicon materials and thus I could not provide further comment on this. Regarding the design, generally we are referring FPGA design ie HDL coding. If you would like to check if your HDL design can be implemented using a specific FPGA, you could use the Quartus Prime software and run through compilation to verify that.

Regarding the licensing management, sorry as I do not have visibility into it and could not really comment further. Generally we would address licensing inquiries related to FPGA software and IP in this forum. Sorry for the inconvenience.

Please let me know if there is any concern. Thank you.

Best regards,

Chee Pin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Chee Pin,

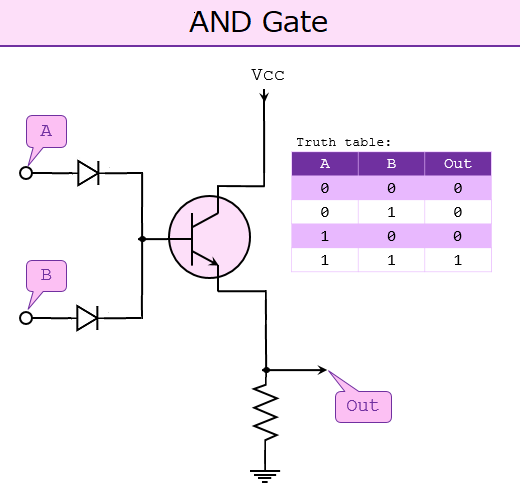

I drew an AND circuit with a transistor. Only if both inputs A and B create enough voltage and current to switch the transistor on, the output will be 1. Could this be a new type of AND circuit? Moreover, I think it is how AND logic applied to a quantum logic gate, as explained in the paper. I wonder if we can implement it to FGPA directly? Or do we need another layer of a semiconductor like GaN on Silicon FGPA board?

Thank you,

Ryoji

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Ryoji,

Thanks for your update. Sorry as I am not really familiar with low level logic design and thus could not really comment on your circuitry. Sorry for the inconvenience.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Chee Pin,

It is a pity that you can not answer my low-level question. But thank you for having some communication here. If you find something related to mine, I would like to know any updates. Thank you again,

Ryoji

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Sorry for all the inconvenience.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your understanding.

This thread will be transitioned to community support. If you have a new question, feel free to open a new thread to get the support from Intel experts. Otherwise, the community users will continue to help you on this thread. Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Dear Chee Pin,

Thank you for your support. Even if it is not an efficient way of the lowest level design, I placed this document on my project on Github along with software development, which would facilitate to issue a global single currency. If you are interested in joining any of those even in your own private time, it must be so helpful. Please check it out here.

Regards,

Ryoji

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page