- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Everyone,

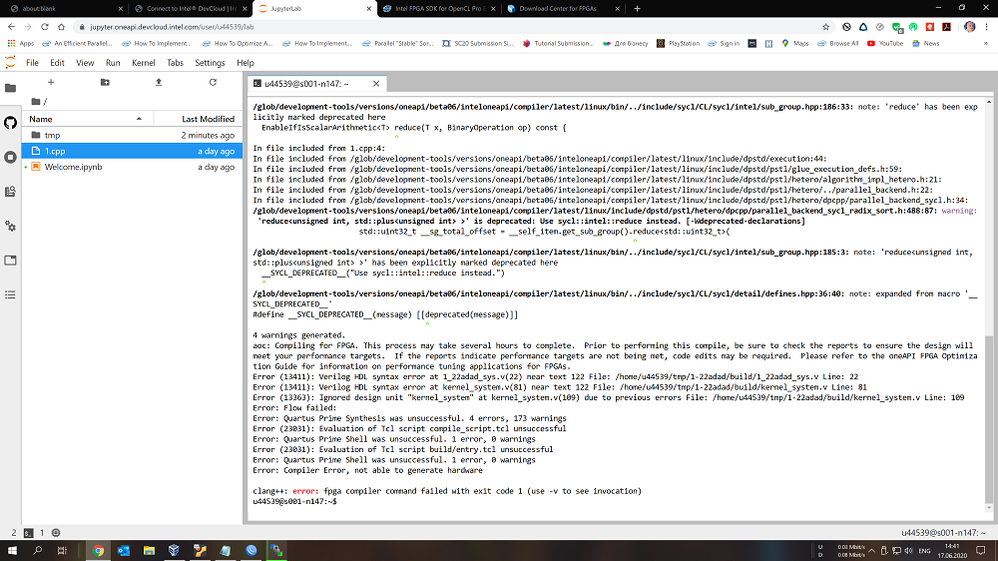

For a few last days long, I'm no longer able to compile and run my code in Intel DevCloud for oneAPI projects.

The attempts to compile and run my code typically end up with the following error message:

I would kindly appreciate for any assistance. Please help me to solve this problem. My DevCloud account id is u39016.

Thanks in advance,

Arthur.

- Tags:

- General Support

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for reaching out.

You can compile and run the oneAPI samples on FPGA platform in Intel Devcloud.Kindly make sure you use the below commands to compile and run the samples.

build_fpga_emu.sh

source /opt/intel/inteloneapi/setvars.sh make fpga_emu -f Makefile.fpga

run_fpga_emu.sh

make run_emu -f Makefile.fpga

Try this and let us know the updates.

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for reaching out.

You can compile and run the oneAPI samples on FPGA platform in Intel Devcloud.Kindly make sure you use the below commands to compile and run the samples.

build_fpga_emu.sh

source /opt/intel/inteloneapi/setvars.sh make fpga_emu -f Makefile.fpga

run_fpga_emu.sh

make run_emu -f Makefile.fpga

Try this and let us know the updates.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, JananiC_Intel

Yes, exactly it works for me, *BUT* it does *NOT* work when compiling this code for Intel PAC card.

Arthur,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Here's what I'm doing:

source /opt/intel/inteloneapi/setvars.sh --force

make run_hw -f Makefile.fpga

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

It normally compiles it with the following commands:

dpcpp -O2 -g -std=c++17 -fintelfpga -c src/simple-add-usm.cpp -o a.o -DFPGA=1

dpcpp -O2 -g -std=c++17 -fintelfpga a.o -o simple-add-usm.fpga -Xshardware

2. Also, I've got a question for you if can I compile my code for Intel PAC card hardware offline (e.g. on-premises) without Intel PAC card installed ?

Could you please guide me how to do that ?

Arthur,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I'm sorry to inform you that this didn't work. First I've tried to compile of the samples for Intel PAC board and it finished compilation successfully, *BUT* when I tried to compile my project for Intel PAC hardware, the compilation ended up with the same error:

Error (170143): Final fitting attempt was unsuccessful

Error: An error occurred during routing

Error: Quartus Prime Fitter was unsuccessful. 2 errors, 675 warnings

Error (23031): Evaluation of Tcl script compile_script.tcl unsuccessful

Error: Quartus Prime Shell was unsuccessful. 1 error, 0 warnings

Error (23031): Evaluation of Tcl script build/entry.tcl unsuccessful

Error: Quartus Prime Shell was unsuccessful. 1 error, 0 warnings

Error: Compiler Error, not able to generate hardware

clang++: error: fpga compiler command failed with exit code 1 (use -v to see invocation)

Makefile:19: recipe for target 'fpga' failed

make: *** [fpga] Error 1

Looking forward to your reply and the following critical issue resolution.

Arthur,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for the update.

In Datacenter devcloud we have FPGA emulator and we do not have PAC in it.

Could you let us know which devcloud are you using(Datacenter/FPGA)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I'm using Intel DevCloud for Intel oneAPI projects. Previously I could compile and run my CL/SYCL program on Intel PAC Platform, but now I experience these difficulties. Also, as I've inspected the following issue, the quartus_fit process crashes when an amount of reserved virtual memory exceeds 16GiB ~ 16384 MB for this process.

Looking forward for this issue resolution as soon as possible :)

Arthur,

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

As your issue is related to FPGA , we are moving your case to FPGA forum for quicker response.

Thanks

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Janani,

Now I am really confused. I thought this is THE FPGA FORUM for High Level Design. Please stop this practice of bouncing forum threads. Other users are interested in the solutions to the questions,

Just my 2c worth.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

May I know if you are able to share with me your source code so that I can debug it to see if it is related to the design not able to fit into the FPGA or due to the system memory issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have the same problem. Have you found a solution yet Arthur? The solution suggested above by Janani only applies to the emulator.

Marcus

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page