- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

We ran a typical hello world example with aoc. By observing the commands in quartus_sh_compile.log, e.g. quartus_sh xxxx, we try to reproduce the same results by doing the same in Quartus. However, we are unable to do so. We compare the log to see what are the differences.

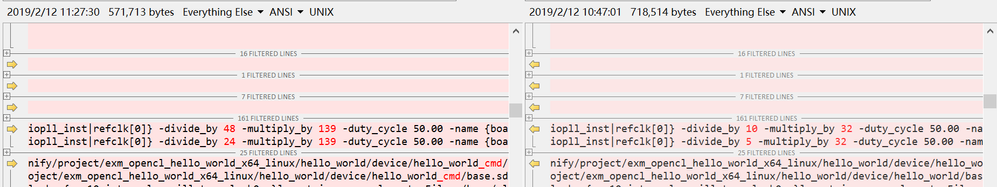

The main and earliest difference was this below.

The log on the right is the original. The PLL clock ratio parameters are different when we rerun it. (See the one on the left)

Is there something we missed?

thanks

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, we just used a hello world downloaded from the Intel website. The code is as attached.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Intel OpenCL compilation flow includes several attempts to improve kernel clock frequency in post_flow.tcl calling the PLL frequency adjustment script: source "$sdk_root/ip/board/bsp/adjust_plls.tcl". Running this script may result in different PLL settings depending on primarily utilizaiton of FPGA and speedgrade. If nothing has changed in your compiles including your CPU, this is indeed strange result. But in general, you may have different number of workgroups or compute units in FPGA. As the utilization of FPGA grows the maximum frequency tends to go down which may explain the different multiply and divide ratio. If your applicaition requires a fixed repeatable frequency it is quite easy to change the script to your local copy which does only one attempt. BTW this will save you some compile time too.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks "Doc"! That explains a lot. Let me go check this out and report back!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, we found 1 occurence of the adjust_pll.tcl in the the post_flow_pr.tcl.

source $::env(INTELFPGAOCLSDKROOT)/ip/board/bsp/adjust_plls_a10.tcl

But after commenting it out, it seems like the pll changes are made much earlier (before even running this script). However, in the pre_flow tcl, we can't find any mention of adjust_plls tcl anywhere.

Any idea how it is linked?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page