- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I am porting my OpenCL design from Arria-10 to Stratix-10 device. On A10 FPGA (1150 device), the best fmax was around 210MHz, however, on Stratix-10 FPGA (2800 device), the best fmax was around 250MHz. The improvement in Fmax was very limited. The same code was used here, and the resource utilization on S10 are 49%(logic), 25%(RAM block) and 3%(DSP).

In the report.html file, the Fmax estimated was around 480MHz.

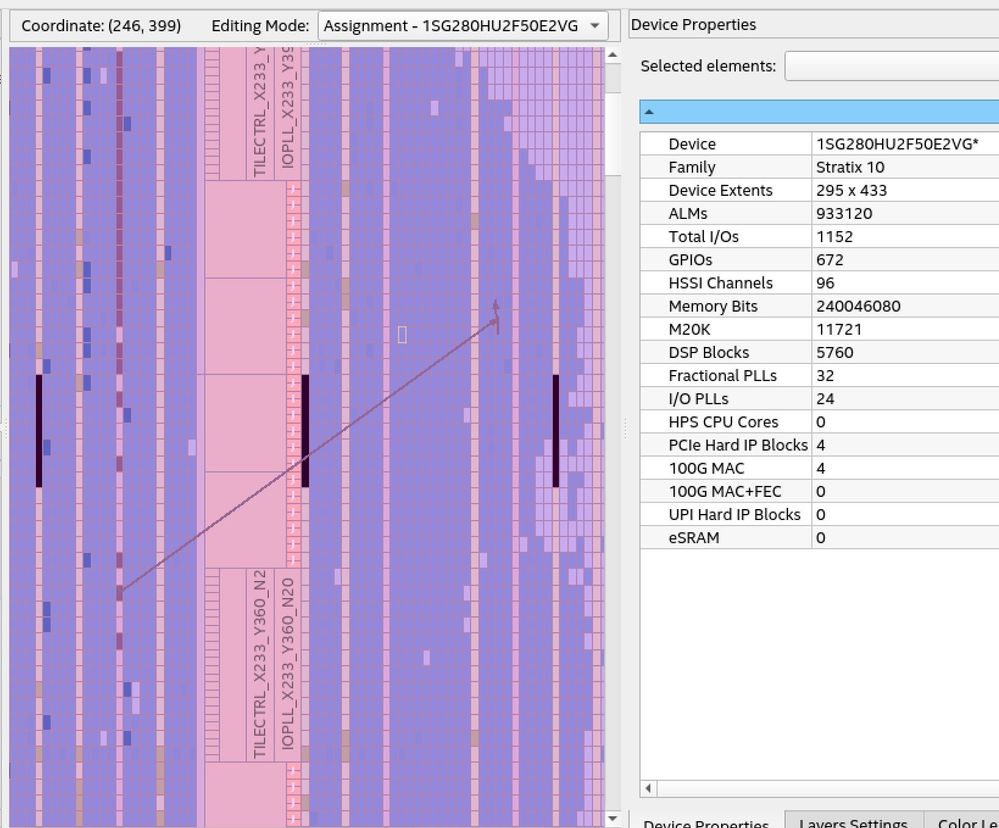

I reported the critical path by using the Timing Analyzer and found that the critical path passes through a region of PLL blocks as follow:

Is this caused by the long routing path ? How could I identify the real cause of the low fmax problem ?

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi ,

There are a variety of methods which can be used to improve the fmax.

It depends on how the code has been written and what and all best practices have been used.

Please refer the document below and compare with the code base and let us know if you can incorporate any of the suggestions to improve the performance.

Thanks and Regards

Anil

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page