- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello All,

This might be a known problem. It looks like AXI Translator module has a bug. When you pick AXI4-Lite on master side AXI Translator expects that RID and BID signals will be set by a module connected to AXI4-Lite but AXI4-Lite doesn't have these signals and that is a responsibility of translator to set it.

I use AXI translator for connecting my AXI4-Lite slave block to HPS (I have Cyclone V FPGA). Since these signals remain not connected any access by software running on HPS hangs the system.

ARM's AXI specification explains translation process in detail so AXI Translator block just doesn't comply it.

PS1: I made a quick experiment and changed a system generated by QSYS so it picks BID and RID from AWID and ARID respectively and this solves the problem.

PS2: I suspect previous versions also have this issue.

Thanks,

Stepan

Link Copied

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I could not find any significant difference from the waveform diagram in modelsim. Perhaps you could help to share screenshot on it? Could you share both of your projects (hang and no hang) so I could duplicate the issue?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a lot for reply.

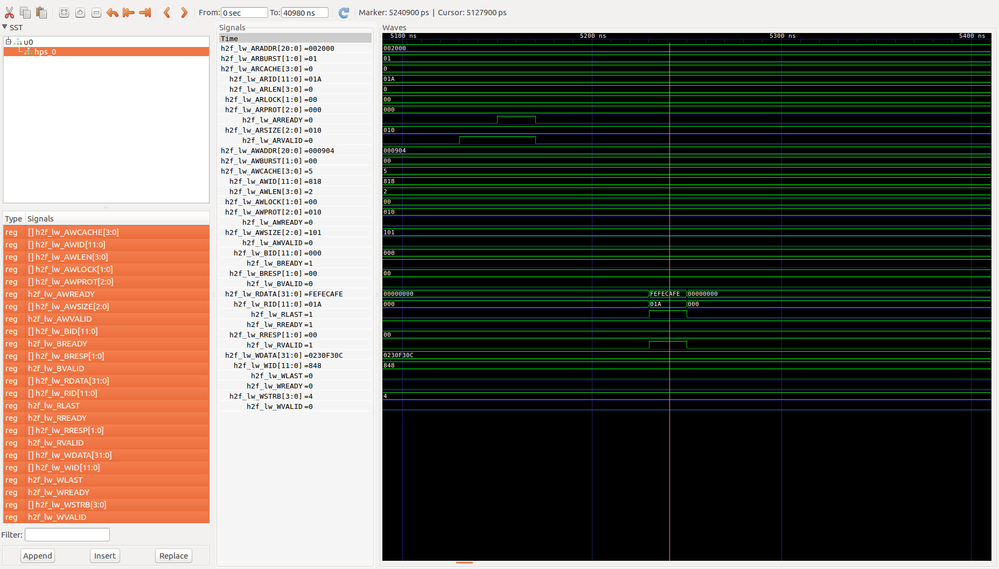

Here are waveforms I captured with SignalTap.

Read transaction, no hang case, when translating to AXI4:

Notice RID signal is set to ARID.

Read transaction, hang case, when translating to AXI4-Lite:

See RID remains zero. Both RID and BID are not connected inside of the translator when translating to AXI4-Lite.

See axi4lite_quick_fix file with a hacky fix to my top of QSYS generated block. Unfortunately I cannot share whole design.

To reproduce you need to run Platform Designer, instantiate HPS, then instantiate AXI translator, connect its slave side to AXI master on HPS and export master side as AXI4-Lite. You'll notice that RID and BID signals are not exported which is correct because AXI4-Lite doesn't use it, however AXI translator doesn't handle these signals correctly for HPS side. That's why it hangs when you try to access MMIO range.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Sorry that the case had been idling for quite sometimes. Do you able to solve the issue?

Is there any help still needed from your side?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We do not receive any response from you to the previous question/reply/answer that I have provided. Please post a response in the next 15 days to allow me to continue to support you. After 15 days, this thread will be transitioned to community support. The community users will be able to help you with your follow-up questions.

Best Regards,

Shyan Yew

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Printer Friendly Page